Other Parts Discussed in Thread: SYSBIOS

Tool/software:

Hey folks,

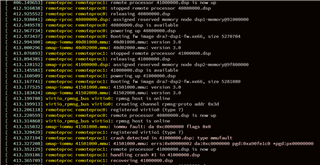

I'm facing some issues while trying to establish IPC between DSP1 and DSP2 in AM5728 Soc, Currently I'm working with the example code provided with the package ipc_3_50_04_08, In this I'm running ex41_forwardmsg example code. So as far I understand the ARM should initialize the IPC memory region and ARM(HOST) will place a packet in DSP1 queue and DSP1 will be processing it and putting it to the IPU1 queue. I took this example code and compiled it for DSP1 and DSP2 while making slight modifications on DSP1 code to attach to DSP2 rather than IPU1 given in the example. Now I run the host application and loaded the binaries to DSP1 and DSP2 core sequentially after loading program to DSP1 after this I get an error code of (-1) which corresponds to "Ipc_E_FAIL" in Ipc_attach() function. If my understanding is correct, This error will come if the host processor has not initialized the shared memory or not called Ipc_start() at the beginning. But even though I started the host application first and DSP1 next and at last I loaded DSP2 I'm still getting this error message. In order to test if ARM->DSP1 and ARM->DSP2 is working I used the ex02_messageq example provided and it works!!. Please point out if I'm doing something wrong. My final requirement is I should be able to send packet from ARM to DSP1 and DSP1 to DSP2.

Attaching files that may help to root cause the issue....

DSP1.cfg

var Edma = xdc.loadPackage ("ti.sdo.edma3.drv.sample");

var drv = xdc.loadPackage ("ti.sdo.edma3.drv");

var rm = xdc.loadPackage ("ti.sdo.edma3.rm");

var Memory = xdc.useModule('xdc.runtime.Memory');

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Event = xdc.useModule('ti.sysbios.knl.Event');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var HeapBuf = xdc.useModule('ti.sysbios.heaps.HeapBuf');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var Idle = xdc.useModule('ti.sysbios.knl.Idle');

var Log = xdc.useModule('xdc.runtime.Log');

var Diags = xdc.useModule('xdc.runtime.Diags');

var C64_Hwi = xdc.useModule ("ti.sysbios.family.c64p.Hwi");

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var ECM = xdc.useModule ("ti.sysbios.family.c64p.EventCombiner");

var IntXbar = xdc.useModule('ti.sysbios.family.shared.vayu.IntXbar');

var core = xdc.useModule('ti.sysbios.hal.Core');

var halCache = xdc.useModule('ti.sysbios.hal.Cache');

var Hwi = xdc.useModule('ti.sysbios.hal.Hwi');

var Clock = xdc.useModule('ti.sysbios.knl.Clock');

//var System = xdc.useModule('xdc.runtime.System');

//var SysStd = xdc.useModule('xdc.runtime.SysStd');

//System.SupportProxy = SysStd;

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Clock = xdc.useModule('ti.sysbios.knl.Clock');

var Swi = xdc.useModule('ti.sysbios.knl.Swi');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var Hwi = xdc.useModule('ti.sysbios.hal.Hwi');

var Settings = xdc.useModule('ti.sysbios.posix.Settings');

var HeapMultiBuf = xdc.useModule('ti.sysbios.heaps.HeapMultiBuf');

ECM.eventGroupHwiNum[0] = 7;

ECM.eventGroupHwiNum[1] = 8;

Program.sectMap[".tracebuf"] = Program.platform.dataMemory;

/* Use SysMin because trace buffer address is required for Linux/QNX

* trace debug driver, plus provides better performance.

*/

var System = xdc.useModule('xdc.runtime.System');

var SysMin = xdc.useModule('ti.trace.SysMin');

System.SupportProxy = SysMin;

SysMin.bufSize = 0x8000;

/* Set CPU Frequency */

BIOS.cpuFreq.lo = 750000000;

BIOS.cpuFreq.hi = 0;

/* default memory heap */

var Memory = xdc.useModule('xdc.runtime.Memory');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var heapMemParams = new HeapMem.Params();

heapMemParams.size = 0x1400000;

Memory.defaultHeapInstance = HeapMem.create(heapMemParams);

var HeapBufMP = xdc.useModule('ti.sdo.ipc.heaps.HeapBufMP');

/* ================ Driver configuration ================ */

/* Load and use the PCIE packages */

var socType = "am572x";

var Pcie = xdc.loadPackage('ti.drv.pcie');

/* Enable only if soc-specific library should be used */

/* Pcie.Settings.socType = socType; */ /* use soc/am572x/src/pcie_soc.c */

/* Load the I2C package - required by board */

var I2c = xdc.loadPackage('ti.drv.i2c');

I2c.Settings.socType = socType;

/* Load the uart package -- required by board */

var Uart = xdc.loadPackage('ti.drv.uart');

Uart.Settings.socType = socType;

/* Load the gpio package */

var Gpio = xdc.loadPackage('ti.drv.gpio');

Gpio.Settings.socType = socType;

/* Load the Board package and set the board name */

var Board = xdc.loadPackage('ti.board');

Board.Settings.boardName = "evmAM572x";

/* Load the osal package -- required by board & interrupt example */

var osType = "tirtos";

var Osal = xdc.loadPackage('ti.osal');

Osal.Settings.osType = osType;

Osal.Settings.socType = socType;

/*use CSL package*/

var Csl = xdc.loadPackage('ti.csl');

Csl.Settings.deviceType = socType;

/* Load the MMCSD package */

var Mmcsd = xdc.loadPackage('ti.drv.mmcsd');

Mmcsd.Settings.enableProfiling = false;

Mmcsd.Settings.useDma = "false";

Mmcsd.Settings.socType= socType;

/* ================ Driver configuration ================ */

/*

* ======== IPC Configuration ========

*/

xdc.useModule('ti.ipc.ipcmgr.IpcMgr');

Program.argSize = 100; /* minimum size */

Program.stack = 0x80000;

/* create a heap for MessageQ messages */

var HeapBuf = xdc.useModule('ti.sysbios.heaps.HeapBuf');

var params = new HeapBuf.Params;

params.align = 8;

params.blockSize = 512;

params.numBlocks = 256;

var msgHeap = HeapBuf.create(params);

var MessageQ = xdc.useModule('ti.sdo.ipc.MessageQ');

MessageQ.registerHeapMeta(msgHeap, 0);

/* Setup MessageQ transport */

var VirtioSetup = xdc.useModule('ti.ipc.transports.TransportRpmsgSetup');

MessageQ.SetupTransportProxy = VirtioSetup;

/* Setup NameServer remote proxy */

var NameServer = xdc.useModule("ti.sdo.utils.NameServer");

var NsRemote = xdc.useModule("ti.ipc.namesrv.NameServerRemoteRpmsg");

NameServer.SetupProxy = NsRemote;

/* Enable Memory Translation module that operates on the BIOS Resource Table */

var Resource = xdc.useModule('ti.ipc.remoteproc.Resource');

Resource.loadSegment = Program.platform.codeMemory;

/* Override default resource table to add CMEM memory section*/

Resource.customTable = true;

/* load the configuration shared across cores */

Program.global.procName = "DSP1";

/* configure processor names */

var procNameAry = ["HOST", "IPU2", "IPU1", "DSP2", "DSP1"];

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

MultiProc.setConfig(Program.global.procName, procNameAry);

var BIOS = xdc.useModule('ti.sysbios.BIOS');

BIOS.addUserStartupFunction('&IpcMgr_ipcStartup');

/* Add Shared Region module */

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

/*

* ======== Instrumentation Configuration ========

*/

/* system logger */

var LoggerSys = xdc.useModule('xdc.runtime.LoggerSys');

var LoggerSysParams = new LoggerSys.Params();

var Defaults = xdc.useModule('xdc.runtime.Defaults');

Defaults.common$.logger = LoggerSys.create(LoggerSysParams);

/* enable runtime Diags_setMask() for non-XDC spec'd modules */

var Diags = xdc.useModule('xdc.runtime.Diags');

Diags.setMaskEnabled = true;

/* override diags mask for selected modules */

xdc.useModule('xdc.runtime.Main');

Diags.setMaskMeta("xdc.runtime.Main",

Diags.ENTRY | Diags.EXIT | Diags.INFO | Diags.USER1, Diags.RUNTIME_ON);

var Registry = xdc.useModule('xdc.runtime.Registry');

Registry.common$.diags_ENTRY = Diags.RUNTIME_OFF;

Registry.common$.diags_EXIT = Diags.RUNTIME_OFF;

Registry.common$.diags_INFO = Diags.RUNTIME_OFF;

Registry.common$.diags_USER1 = Diags.RUNTIME_OFF;

Registry.common$.diags_LIFECYCLE = Diags.RUNTIME_OFF;

Registry.common$.diags_STATUS = Diags.RUNTIME_OFF;

var Main = xdc.useModule('xdc.runtime.Main');

Main.common$.diags_ASSERT = Diags.ALWAYS_ON;

Main.common$.diags_INTERNAL = Diags.ALWAYS_ON;

Program.sectMap[".test_data"] = "L2SRAM";

Program.sectMap[".mem_buff"] = "EXT_HEAP";

Program.sectMap[".adc_buff"] = "EXT_HEAP";

DSP1_config.bld

var Build = xdc.useModule('xdc.bld.BuildEnvironment');

var evmDRA7XX_ExtMemMapDsp = {

EXT_CODE: {

name: "EXT_CODE",

base: 0x95000000,

len: 0x00100000,

space: "code",

access: "RWX"

},

EXT_DATA: {

name: "EXT_DATA",

base: 0x95100000,

len: 0x02000000,

space: "data",

access: "RW"

},

EXT_HEAP: {

name: "EXT_HEAP",

base: 0x80000000,

len: 0x09000000,

space: "data",

access: "RW"

},

EXC_DATA: {

name: "EXC_DATA",

base: 0x9F060000,

len: 0x00010000,

space: "data",

access: "RW"

},

PM_DATA: {

name: "PM_DATA",

base: 0x9F070000,

len: 0x00020000,

space: "data",

access: "RWX" /* should this have execute perm? */

},

};

Build.platformTable["ti.platforms.evmDRA7XX:dsp"] = {

externalMemoryMap: [

[ "EXT_CODE", evmDRA7XX_ExtMemMapDsp.EXT_CODE ],

[ "EXT_DATA", evmDRA7XX_ExtMemMapDsp.EXT_DATA ],

[ "EXT_HEAP", evmDRA7XX_ExtMemMapDsp.EXT_HEAP ],

[ "EXC_DATA", evmDRA7XX_ExtMemMapDsp.EXC_DATA ],

[ "PM_DATA", evmDRA7XX_ExtMemMapDsp.PM_DATA ],

],

codeMemory: "EXT_CODE",

dataMemory: "EXT_DATA",

stackMemory: "EXT_DATA",

};

rsc_table_dsp1.h

#ifndef _RSC_TABLE_DSP_H_

#define _RSC_TABLE_DSP_H_

#include <ti/ipc/remoteproc/rsc_types.h>

/* DSP Memory Map */

#define L4_DRA7XX_BASE 0x4A000000

#define L4_PERIPHERAL_L4CFG (L4_DRA7XX_BASE)

#define DSP_PERIPHERAL_L4CFG 0x4A000000

#define L4_PERIPHERAL_L4PER1 0x48000000

#define DSP_PERIPHERAL_L4PER1 0x48000000

#define L4_PERIPHERAL_L4PER2 0x48400000

#define DSP_PERIPHERAL_L4PER2 0x48400000

#define L4_PERIPHERAL_L4PER3 0x48800000

#define DSP_PERIPHERAL_L4PER3 0x48800000

#define L4_PERIPHERAL_L4EMU 0x54000000

#define DSP_PERIPHERAL_L4EMU 0x54000000

#define L3_PERIPHERAL_DMM 0x4E000000

#define DSP_PERIPHERAL_DMM 0x4E000000

#define L3_TILER_MODE_0_1 0x60000000

#define DSP_TILER_MODE_0_1 0x60000000

#define L3_TILER_MODE_2 0x70000000

#define DSP_TILER_MODE_2 0x70000000

#define L3_TILER_MODE_3 0x78000000

#define DSP_TILER_MODE_3 0x78000000

//////////

#define L3_PERIPHERAL_EDMA 0x43300000

#define DSP_PERIPHERAL_EDMA 0x43300000

#define L3_PCIE_SS1_CONFIG_REG_BASE 0x51000000

#define DSP_PCIE_SS1_CONFIG_REG_BASE 0x51000000

#define L3_PCIE_SS1_CONFIG_SPACE_BASE 0x20000000

#define DSP_PCIE_SS1_CONFIG_SPACE_BASE 0x20000000

//////////////

#define DSP_MEM_TEXT 0x95000000

/* Co-locate alongside TILER region for easier flushing */

#define DSP_MEM_IOBUFS 0xBA300000

#define DSP_MEM_DATA 0x95100000

#define DSP_MEM_HEAP 0x80000000

#define DSP_MEM_IPC_DATA 0x9F000000

#define DSP_MEM_IPC_VRING 0x99000000

#define DSP_MEM_RPMSG_VRING0 0x99000000

#define DSP_MEM_RPMSG_VRING1 0x99004000

#define DSP_MEM_VRING_BUFS0 0x99040000

#define DSP_MEM_VRING_BUFS1 0x99080000

#define DSP_MEM_IPC_VRING_SIZE SZ_1M

#define DSP_MEM_IPC_DATA_SIZE SZ_1M

#define DSP_MEM_TEXT_SIZE SZ_1M

#define DSP_MEM_DATA_SIZE (SZ_1M * 32)

#define DSP_MEM_HEAP_SIZE (SZ_1M * 144)

#define DSP_MEM_IOBUFS_SIZE (SZ_1M * 90)

/* NOTE: Make sure this matches what is configured in the linux device tree */

#define DSP_CMEM_IOBUFS 0xc0000000

#define PHYS_CMEM_IOBUFS 0xc0000000

#define DSP_CMEM_IOBUFS_SIZE (SZ_1M * 192)

/*

* Assign fixed RAM addresses to facilitate a fixed MMU table.

*/

#define VAYU_DSP_1

/* See CMA BASE addresses in Linux side: arch/arm/mach-omap2/remoteproc.c */

#if defined(VAYU_DSP_1)

#define PHYS_MEM_IPC_VRING 0x91000000

#elif defined(VAYU_DSP_2)

#define PHYS_MEM_IPC_VRING 0x9F000000

#endif

/* Need to be identical to that of IPU */

#define PHYS_MEM_IOBUFS 0xBA300000

/*

* Sizes of the virtqueues (expressed in number of buffers supported,

* and must be power of 2)

*/

#define DSP_RPMSG_VQ0_SIZE 256

#define DSP_RPMSG_VQ1_SIZE 256

/* flip up bits whose indices represent features we support */

#define RPMSG_DSP_C0_FEATURES 1

struct my_resource_table {

struct resource_table base;

UInt32 offset[21]; /* Should match 'num' in actual definition */

/* rpmsg vdev entry */

struct fw_rsc_vdev rpmsg_vdev;

struct fw_rsc_vdev_vring rpmsg_vring0;

struct fw_rsc_vdev_vring rpmsg_vring1;

/* text carveout entry */

struct fw_rsc_carveout text_cout;

/* data carveout entry */

struct fw_rsc_carveout data_cout;

/* heap carveout entry */

struct fw_rsc_carveout heap_cout;

/* ipcdata carveout entry */

struct fw_rsc_carveout ipcdata_cout;

/* trace entry */

struct fw_rsc_trace trace;

/* devmem entry */

struct fw_rsc_devmem devmem0;

/* devmem entry */

struct fw_rsc_devmem devmem1;

/* devmem entry */

struct fw_rsc_devmem devmem2;

/* devmem entry */

struct fw_rsc_devmem devmem3;

/* devmem entry */

struct fw_rsc_devmem devmem4;

/* devmem entry */

struct fw_rsc_devmem devmem5;

/* devmem entry */

struct fw_rsc_devmem devmem6;

/* devmem entry */

struct fw_rsc_devmem devmem7;

/* devmem entry */

struct fw_rsc_devmem devmem8;

/* devmem entry */

struct fw_rsc_devmem devmem9;

/* devmem entry */

struct fw_rsc_devmem devmem10;

/* devmem entry */

struct fw_rsc_devmem devmem11;

/* devmem entry */

struct fw_rsc_devmem devmem12;

/* devmem entry */

struct fw_rsc_devmem devmem13;

/* devmem entry */

struct fw_rsc_devmem devmem14;

};

extern char ti_trace_SysMin_Module_State_0_outbuf__A;

#define TRACEBUFADDR (UInt32) & ti_trace_SysMin_Module_State_0_outbuf__A

#pragma DATA_SECTION(ti_ipc_remoteproc_ResourceTable, ".resource_table")

#pragma DATA_ALIGN(ti_ipc_remoteproc_ResourceTable, 4096)

struct my_resource_table ti_ipc_remoteproc_ResourceTable = {

1, /* we're the first version that implements this */

21, /* number of entries in the table */

0,

0, /* reserved, must be zero */

/* offsets to entries */

{

offsetof(struct my_resource_table, rpmsg_vdev),

offsetof(struct my_resource_table, text_cout),

offsetof(struct my_resource_table, data_cout),

offsetof(struct my_resource_table, heap_cout),

offsetof(struct my_resource_table, ipcdata_cout),

offsetof(struct my_resource_table, trace),

offsetof(struct my_resource_table, devmem0),

offsetof(struct my_resource_table, devmem1),

offsetof(struct my_resource_table, devmem2),

offsetof(struct my_resource_table, devmem3),

offsetof(struct my_resource_table, devmem4),

offsetof(struct my_resource_table, devmem5),

offsetof(struct my_resource_table, devmem6),

offsetof(struct my_resource_table, devmem7),

offsetof(struct my_resource_table, devmem8),

offsetof(struct my_resource_table, devmem9),

offsetof(struct my_resource_table, devmem10),

offsetof(struct my_resource_table, devmem11),

offsetof(struct my_resource_table, devmem12),

offsetof(struct my_resource_table, devmem13),

offsetof(struct my_resource_table, devmem14),

},

/* rpmsg vdev entry */

{

TYPE_VDEV,

VIRTIO_ID_RPMSG,

0,

RPMSG_DSP_C0_FEATURES,

0,

0,

0,

2,

{0, 0},

/* no config data */

},

/* the two vrings */

{DSP_MEM_RPMSG_VRING0, 4096, DSP_RPMSG_VQ0_SIZE, 1, 0},

{DSP_MEM_RPMSG_VRING1, 4096, DSP_RPMSG_VQ1_SIZE, 2, 0},

{

TYPE_CARVEOUT, DSP_MEM_TEXT, 0, DSP_MEM_TEXT_SIZE, 0, 0, "DSP_MEM_TEXT",

},

{

TYPE_CARVEOUT, DSP_MEM_DATA, 0, DSP_MEM_DATA_SIZE, 0, 0, "DSP_MEM_DATA",

},

{

TYPE_CARVEOUT, DSP_MEM_HEAP, 0, DSP_MEM_HEAP_SIZE, 0, 0, "DSP_MEM_HEAP",

},

{

TYPE_CARVEOUT, DSP_MEM_IPC_DATA, 0, DSP_MEM_IPC_DATA_SIZE, 0, 0,

"DSP_MEM_IPC_DATA",

},

{

TYPE_TRACE, TRACEBUFADDR, 0x8000, 0, "trace:dsp",

},

{

TYPE_DEVMEM, DSP_MEM_IPC_VRING, PHYS_MEM_IPC_VRING,

DSP_MEM_IPC_VRING_SIZE, 0, 0, "DSP_MEM_IPC_VRING",

},

{

TYPE_DEVMEM, DSP_MEM_IOBUFS, PHYS_MEM_IOBUFS, DSP_MEM_IOBUFS_SIZE, 0, 0,

"DSP_MEM_IOBUFS",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_0_1, L3_TILER_MODE_0_1, SZ_256M, 0, 0,

"DSP_TILER_MODE_0_1",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_2, L3_TILER_MODE_2, SZ_128M, 0, 0,

"DSP_TILER_MODE_2",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_3, L3_TILER_MODE_3, SZ_128M, 0, 0,

"DSP_TILER_MODE_3",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4CFG, L4_PERIPHERAL_L4CFG, SZ_16M, 0, 0,

"DSP_PERIPHERAL_L4CFG",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER1, L4_PERIPHERAL_L4PER1, SZ_2M, 0, 0,

"DSP_PERIPHERAL_L4PER1",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER2, L4_PERIPHERAL_L4PER2, SZ_4M, 0, 0,

"DSP_PERIPHERAL_L4PER2",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER3, L4_PERIPHERAL_L4PER3, SZ_8M, 0, 0,

"DSP_PERIPHERAL_L4PER3",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4EMU, L4_PERIPHERAL_L4EMU, SZ_16M, 0, 0,

"DSP_PERIPHERAL_L4EMU",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_DMM, L3_PERIPHERAL_DMM, SZ_1M, 0, 0,

"DSP_PERIPHERAL_DMM",

},

{

TYPE_DEVMEM, DSP_CMEM_IOBUFS, PHYS_CMEM_IOBUFS, DSP_CMEM_IOBUFS_SIZE, 0,

0, "DSP_CMEM_IOBUFS",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_EDMA, L3_PERIPHERAL_EDMA, SZ_1M*3, 0,

0, "DSP_EDMA",

},

{

TYPE_DEVMEM, DSP_PCIE_SS1_CONFIG_REG_BASE, L3_PCIE_SS1_CONFIG_REG_BASE, SZ_8M, 0,

0, "DSP_PCIE_REG_BASE",

},

{

TYPE_DEVMEM, DSP_PCIE_SS1_CONFIG_SPACE_BASE, L3_PCIE_SS1_CONFIG_SPACE_BASE, SZ_256M, 0,

0, "DSP_PCIE_CONFIG_BASE",

},

};

#endif /* _RSC_TABLE_DSP_H_ */

----------------------------------------------------------------------------------------------------------------------------

DSP2.cfg

var Edma = xdc.loadPackage ("ti.sdo.edma3.drv.sample");

var drv = xdc.loadPackage ("ti.sdo.edma3.drv");

var rm = xdc.loadPackage ("ti.sdo.edma3.rm");

var Memory = xdc.useModule('xdc.runtime.Memory');

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Event = xdc.useModule('ti.sysbios.knl.Event');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var HeapBuf = xdc.useModule('ti.sysbios.heaps.HeapBuf');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var Idle = xdc.useModule('ti.sysbios.knl.Idle');

var Log = xdc.useModule('xdc.runtime.Log');

var Diags = xdc.useModule('xdc.runtime.Diags');

var C64_Hwi = xdc.useModule ("ti.sysbios.family.c64p.Hwi");

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var ECM = xdc.useModule ("ti.sysbios.family.c64p.EventCombiner");

var IntXbar = xdc.useModule('ti.sysbios.family.shared.vayu.IntXbar');

var core = xdc.useModule('ti.sysbios.hal.Core');

var halCache = xdc.useModule('ti.sysbios.hal.Cache');

var Hwi = xdc.useModule('ti.sysbios.hal.Hwi');

var Clock = xdc.useModule('ti.sysbios.knl.Clock');

//var System = xdc.useModule('xdc.runtime.System');

//var SysStd = xdc.useModule('xdc.runtime.SysStd');

//System.SupportProxy = SysStd;

var BIOS = xdc.useModule('ti.sysbios.BIOS');

var Clock = xdc.useModule('ti.sysbios.knl.Clock');

var Swi = xdc.useModule('ti.sysbios.knl.Swi');

var Task = xdc.useModule('ti.sysbios.knl.Task');

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

var Hwi = xdc.useModule('ti.sysbios.hal.Hwi');

var Settings = xdc.useModule('ti.sysbios.posix.Settings');

var HeapMultiBuf = xdc.useModule('ti.sysbios.heaps.HeapMultiBuf');

Program.sectMap[".tracebuf"] = Program.platform.dataMemory;

/* Use SysMin because trace buffer address is required for Linux/QNX

* trace debug driver, plus provides better performance.

*/

var System = xdc.useModule('xdc.runtime.System');

var SysMin = xdc.useModule('ti.trace.SysMin');

System.SupportProxy = SysMin;

SysMin.bufSize = 0x8000;

/* Set CPU Frequency */

BIOS.cpuFreq.lo = 750000000;

BIOS.cpuFreq.hi = 0;

/* default memory heap */

var Memory = xdc.useModule('xdc.runtime.Memory');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var heapMemParams = new HeapMem.Params();

heapMemParams.size = 0x1400000;

Memory.defaultHeapInstance = HeapMem.create(heapMemParams);

var HeapBufMP = xdc.useModule('ti.sdo.ipc.heaps.HeapBufMP');

/* ================ Driver configuration ================ */

/* Load and use the PCIE packages */

var socType = "am572x";

var Pcie = xdc.loadPackage('ti.drv.pcie');

/* Enable only if soc-specific library should be used */

/* Pcie.Settings.socType = socType; */ /* use soc/am572x/src/pcie_soc.c */

/* Load the I2C package - required by board */

var I2c = xdc.loadPackage('ti.drv.i2c');

I2c.Settings.socType = socType;

/* Load the uart package -- required by board */

var Uart = xdc.loadPackage('ti.drv.uart');

Uart.Settings.socType = socType;

/* Load the gpio package */

var Gpio = xdc.loadPackage('ti.drv.gpio');

Gpio.Settings.socType = socType;

/* Load the Board package and set the board name */

var Board = xdc.loadPackage('ti.board');

Board.Settings.boardName = "evmAM572x";

/* Load the osal package -- required by board & interrupt example */

var osType = "tirtos";

var Osal = xdc.loadPackage('ti.osal');

Osal.Settings.osType = osType;

Osal.Settings.socType = socType;

/*use CSL package*/

var Csl = xdc.loadPackage('ti.csl');

Csl.Settings.deviceType = socType;

/* Load the MMCSD package */

var Mmcsd = xdc.loadPackage('ti.drv.mmcsd');

Mmcsd.Settings.enableProfiling = false;

Mmcsd.Settings.useDma = "false";

Mmcsd.Settings.socType= socType;

/* ================ Driver configuration ================ */

/*

* ======== IPC Configuration ========

*/

xdc.useModule('ti.ipc.ipcmgr.IpcMgr');

Program.argSize = 100; /* minimum size */

Program.stack = 0x80000;

/* create a heap for MessageQ messages */

var HeapBuf = xdc.useModule('ti.sysbios.heaps.HeapBuf');

var params = new HeapBuf.Params;

params.align = 8;

params.blockSize = 512;

params.numBlocks = 256;

var msgHeap = HeapBuf.create(params);

var MessageQ = xdc.useModule('ti.sdo.ipc.MessageQ');

MessageQ.registerHeapMeta(msgHeap, 0);

/* Setup MessageQ transport */

var VirtioSetup = xdc.useModule('ti.ipc.transports.TransportRpmsgSetup');

MessageQ.SetupTransportProxy = VirtioSetup;

/* Setup NameServer remote proxy */

var NameServer = xdc.useModule("ti.sdo.utils.NameServer");

var NsRemote = xdc.useModule("ti.ipc.namesrv.NameServerRemoteRpmsg");

NameServer.SetupProxy = NsRemote;

/* Enable Memory Translation module that operates on the BIOS Resource Table */

var Resource = xdc.useModule('ti.ipc.remoteproc.Resource');

Resource.loadSegment = Program.platform.codeMemory;

/* Override default resource table to add CMEM memory section*/

Resource.customTable = true;

/* load the configuration shared across cores */

Program.global.procName = "DSP2";

/* configure processor names */

var procNameAry = ["HOST", "IPU2", "IPU1", "DSP2", "DSP1"];

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

MultiProc.setConfig(Program.global.procName, procNameAry);

var BIOS = xdc.useModule('ti.sysbios.BIOS');

BIOS.addUserStartupFunction('&IpcMgr_ipcStartup');

/* Add Shared Region module */

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion');

/*

* ======== Instrumentation Configuration ========

*/

/* system logger */

var LoggerSys = xdc.useModule('xdc.runtime.LoggerSys');

var LoggerSysParams = new LoggerSys.Params();

var Defaults = xdc.useModule('xdc.runtime.Defaults');

Defaults.common$.logger = LoggerSys.create(LoggerSysParams);

/* enable runtime Diags_setMask() for non-XDC spec'd modules */

var Diags = xdc.useModule('xdc.runtime.Diags');

Diags.setMaskEnabled = true;

/* override diags mask for selected modules */

xdc.useModule('xdc.runtime.Main');

Diags.setMaskMeta("xdc.runtime.Main",

Diags.ENTRY | Diags.EXIT | Diags.INFO | Diags.USER1, Diags.RUNTIME_ON);

var Registry = xdc.useModule('xdc.runtime.Registry');

Registry.common$.diags_ENTRY = Diags.RUNTIME_OFF;

Registry.common$.diags_EXIT = Diags.RUNTIME_OFF;

Registry.common$.diags_INFO = Diags.RUNTIME_OFF;

Registry.common$.diags_USER1 = Diags.RUNTIME_OFF;

Registry.common$.diags_LIFECYCLE = Diags.RUNTIME_OFF;

Registry.common$.diags_STATUS = Diags.RUNTIME_OFF;

var Main = xdc.useModule('xdc.runtime.Main');

Main.common$.diags_ASSERT = Diags.ALWAYS_ON;

Main.common$.diags_INTERNAL = Diags.ALWAYS_ON;

Program.sectMap[".test_data"] = "L2SRAM";

Program.sectMap[".mem_buff"] = "EXT_HEAP";

Program.sectMap[".adc_buff"] = "EXT_HEAP";

DSP2_config.bld

var Build = xdc.useModule('xdc.bld.BuildEnvironment');

var evmDRA7XX_ExtMemMapDsp = {

EXT_CODE: {

name: "EXT_CODE",

base: 0x95000000,

len: 0x00100000,

space: "code",

access: "RWX"

},

EXT_DATA: {

name: "EXT_DATA",

base: 0x95100000,

len: 0x02000000,

space: "data",

access: "RW"

},

EXT_HEAP: {

name: "EXT_HEAP",

base: 0xAD800000,

len: 0x09000000,

space: "data",

access: "RW"

},

EXC_DATA: {

name: "EXC_DATA",

base: 0x9F060000,

len: 0x00010000,

space: "data",

access: "RW"

},

PM_DATA: {

name: "PM_DATA",

base: 0x9F070000,

len: 0x00020000,

space: "data",

access: "RWX" /* should this have execute perm? */

},

};

Build.platformTable["ti.platforms.evmDRA7XX:dsp"] = {

externalMemoryMap: [

[ "EXT_CODE", evmDRA7XX_ExtMemMapDsp.EXT_CODE ],

[ "EXT_DATA", evmDRA7XX_ExtMemMapDsp.EXT_DATA ],

[ "EXT_HEAP", evmDRA7XX_ExtMemMapDsp.EXT_HEAP ],

[ "EXC_DATA", evmDRA7XX_ExtMemMapDsp.EXC_DATA ],

[ "PM_DATA", evmDRA7XX_ExtMemMapDsp.PM_DATA ],

],

codeMemory: "EXT_CODE",

dataMemory: "EXT_DATA",

stackMemory: "EXT_DATA",

};

rsc_table_DSP2.h

#ifndef _RSC_TABLE_DSP_H_

#define _RSC_TABLE_DSP_H_

#include <ti/ipc/remoteproc/rsc_types.h>

/* DSP Memory Map */

#define L4_DRA7XX_BASE 0x4A000000

#define L4_PERIPHERAL_L4CFG (L4_DRA7XX_BASE)

#define DSP_PERIPHERAL_L4CFG 0x4A000000

#define L4_PERIPHERAL_L4PER1 0x48000000

#define DSP_PERIPHERAL_L4PER1 0x48000000

#define L4_PERIPHERAL_L4PER2 0x48400000

#define DSP_PERIPHERAL_L4PER2 0x48400000

#define L4_PERIPHERAL_L4PER3 0x48800000

#define DSP_PERIPHERAL_L4PER3 0x48800000

#define L4_PERIPHERAL_L4EMU 0x54000000

#define DSP_PERIPHERAL_L4EMU 0x54000000

#define L3_PERIPHERAL_DMM 0x4E000000

#define DSP_PERIPHERAL_DMM 0x4E000000

#define L3_TILER_MODE_0_1 0x60000000

#define DSP_TILER_MODE_0_1 0x60000000

#define L3_TILER_MODE_2 0x70000000

#define DSP_TILER_MODE_2 0x70000000

#define L3_TILER_MODE_3 0x78000000

#define DSP_TILER_MODE_3 0x78000000

//////////

#define L3_PERIPHERAL_EDMA 0x43300000

#define DSP_PERIPHERAL_EDMA 0x43300000

#define L3_PCIE_SS1_CONFIG_REG_BASE 0x51000000

#define DSP_PCIE_SS1_CONFIG_REG_BASE 0x51000000

#define L3_PCIE_SS1_CONFIG_SPACE_BASE 0x20000000

#define DSP_PCIE_SS1_CONFIG_SPACE_BASE 0x20000000

//////////////

#define DSP_MEM_TEXT 0x95000000

/* Co-locate alongside TILER region for easier flushing */

#define DSP_MEM_IOBUFS 0xBA300000

#define DSP_MEM_DATA 0x95100000

#define DSP_MEM_HEAP 0xAD800000

#define DSP_MEM_IPC_DATA 0x9F000000

#define DSP_MEM_IPC_VRING 0x99000000

#define DSP_MEM_RPMSG_VRING0 0x99000000

#define DSP_MEM_RPMSG_VRING1 0x99004000

#define DSP_MEM_VRING_BUFS0 0x99040000

#define DSP_MEM_VRING_BUFS1 0x99080000

#define DSP_MEM_IPC_VRING_SIZE SZ_1M

#define DSP_MEM_IPC_DATA_SIZE SZ_1M

#define DSP_MEM_TEXT_SIZE SZ_1M

#define DSP_MEM_DATA_SIZE (SZ_1M * 32)

#define DSP_MEM_HEAP_SIZE (SZ_1M * 144)

#define DSP_MEM_IOBUFS_SIZE (SZ_1M * 90)

/* NOTE: Make sure this matches what is configured in the linux device tree */

#define DSP_CMEM_IOBUFS 0xcc000000

#define PHYS_CMEM_IOBUFS 0xcc000000

#define DSP_CMEM_IOBUFS_SIZE (SZ_1M * 192)

/*

* Assign fixed RAM addresses to facilitate a fixed MMU table.

*/

#define VAYU_DSP_2

/* See CMA BASE addresses in Linux side: arch/arm/mach-omap2/remoteproc.c */

#if defined(VAYU_DSP_1)

#define PHYS_MEM_IPC_VRING 0x91000000

#elif defined(VAYU_DSP_2)

#define PHYS_MEM_IPC_VRING 0x9F800000

#endif

/* Need to be identical to that of IPU */

#define PHYS_MEM_IOBUFS 0xBA300000

/*

* Sizes of the virtqueues (expressed in number of buffers supported,

* and must be power of 2)

*/

#define DSP_RPMSG_VQ0_SIZE 256

#define DSP_RPMSG_VQ1_SIZE 256

/* flip up bits whose indices represent features we support */

#define RPMSG_DSP_C0_FEATURES 1

struct my_resource_table {

struct resource_table base;

UInt32 offset[21]; /* Should match 'num' in actual definition */

/* rpmsg vdev entry */

struct fw_rsc_vdev rpmsg_vdev;

struct fw_rsc_vdev_vring rpmsg_vring0;

struct fw_rsc_vdev_vring rpmsg_vring1;

/* text carveout entry */

struct fw_rsc_carveout text_cout;

/* data carveout entry */

struct fw_rsc_carveout data_cout;

/* heap carveout entry */

struct fw_rsc_carveout heap_cout;

/* ipcdata carveout entry */

struct fw_rsc_carveout ipcdata_cout;

/* trace entry */

struct fw_rsc_trace trace;

/* devmem entry */

struct fw_rsc_devmem devmem0;

/* devmem entry */

struct fw_rsc_devmem devmem1;

/* devmem entry */

struct fw_rsc_devmem devmem2;

/* devmem entry */

struct fw_rsc_devmem devmem3;

/* devmem entry */

struct fw_rsc_devmem devmem4;

/* devmem entry */

struct fw_rsc_devmem devmem5;

/* devmem entry */

struct fw_rsc_devmem devmem6;

/* devmem entry */

struct fw_rsc_devmem devmem7;

/* devmem entry */

struct fw_rsc_devmem devmem8;

/* devmem entry */

struct fw_rsc_devmem devmem9;

/* devmem entry */

struct fw_rsc_devmem devmem10;

/* devmem entry */

struct fw_rsc_devmem devmem11;

/* devmem entry */

struct fw_rsc_devmem devmem12;

/* devmem entry */

struct fw_rsc_devmem devmem13;

/* devmem entry */

struct fw_rsc_devmem devmem14;

};

extern char ti_trace_SysMin_Module_State_0_outbuf__A;

#define TRACEBUFADDR (UInt32) & ti_trace_SysMin_Module_State_0_outbuf__A

#pragma DATA_SECTION(ti_ipc_remoteproc_ResourceTable, ".resource_table")

#pragma DATA_ALIGN(ti_ipc_remoteproc_ResourceTable, 4096)

struct my_resource_table ti_ipc_remoteproc_ResourceTable = {

1, /* we're the first version that implements this */

21, /* number of entries in the table */

0,

0, /* reserved, must be zero */

/* offsets to entries */

{

offsetof(struct my_resource_table, rpmsg_vdev),

offsetof(struct my_resource_table, text_cout),

offsetof(struct my_resource_table, data_cout),

offsetof(struct my_resource_table, heap_cout),

offsetof(struct my_resource_table, ipcdata_cout),

offsetof(struct my_resource_table, trace),

offsetof(struct my_resource_table, devmem0),

offsetof(struct my_resource_table, devmem1),

offsetof(struct my_resource_table, devmem2),

offsetof(struct my_resource_table, devmem3),

offsetof(struct my_resource_table, devmem4),

offsetof(struct my_resource_table, devmem5),

offsetof(struct my_resource_table, devmem6),

offsetof(struct my_resource_table, devmem7),

offsetof(struct my_resource_table, devmem8),

offsetof(struct my_resource_table, devmem9),

offsetof(struct my_resource_table, devmem10),

offsetof(struct my_resource_table, devmem11),

offsetof(struct my_resource_table, devmem12),

offsetof(struct my_resource_table, devmem13),

offsetof(struct my_resource_table, devmem14),

},

/* rpmsg vdev entry */

{

TYPE_VDEV,

VIRTIO_ID_RPMSG,

0,

RPMSG_DSP_C0_FEATURES,

0,

0,

0,

2,

{0, 0},

/* no config data */

},

/* the two vrings */

{DSP_MEM_RPMSG_VRING0, 4096, DSP_RPMSG_VQ0_SIZE, 1, 0},

{DSP_MEM_RPMSG_VRING1, 4096, DSP_RPMSG_VQ1_SIZE, 2, 0},

{

TYPE_CARVEOUT, DSP_MEM_TEXT, 0, DSP_MEM_TEXT_SIZE, 0, 0, "DSP_MEM_TEXT",

},

{

TYPE_CARVEOUT, DSP_MEM_DATA, 0, DSP_MEM_DATA_SIZE, 0, 0, "DSP_MEM_DATA",

},

{

TYPE_CARVEOUT, DSP_MEM_HEAP, 0, DSP_MEM_HEAP_SIZE, 0, 0, "DSP_MEM_HEAP",

},

{

TYPE_CARVEOUT, DSP_MEM_IPC_DATA, 0, DSP_MEM_IPC_DATA_SIZE, 0, 0,

"DSP_MEM_IPC_DATA",

},

{

TYPE_TRACE, TRACEBUFADDR, 0x8000, 0, "trace:dsp",

},

{

TYPE_DEVMEM, DSP_MEM_IPC_VRING, PHYS_MEM_IPC_VRING,

DSP_MEM_IPC_VRING_SIZE, 0, 0, "DSP_MEM_IPC_VRING",

},

{

TYPE_DEVMEM, DSP_MEM_IOBUFS, PHYS_MEM_IOBUFS, DSP_MEM_IOBUFS_SIZE, 0, 0,

"DSP_MEM_IOBUFS",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_0_1, L3_TILER_MODE_0_1, SZ_256M, 0, 0,

"DSP_TILER_MODE_0_1",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_2, L3_TILER_MODE_2, SZ_128M, 0, 0,

"DSP_TILER_MODE_2",

},

{

TYPE_DEVMEM, DSP_TILER_MODE_3, L3_TILER_MODE_3, SZ_128M, 0, 0,

"DSP_TILER_MODE_3",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4CFG, L4_PERIPHERAL_L4CFG, SZ_16M, 0, 0,

"DSP_PERIPHERAL_L4CFG",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER1, L4_PERIPHERAL_L4PER1, SZ_2M, 0, 0,

"DSP_PERIPHERAL_L4PER1",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER2, L4_PERIPHERAL_L4PER2, SZ_4M, 0, 0,

"DSP_PERIPHERAL_L4PER2",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4PER3, L4_PERIPHERAL_L4PER3, SZ_8M, 0, 0,

"DSP_PERIPHERAL_L4PER3",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_L4EMU, L4_PERIPHERAL_L4EMU, SZ_16M, 0, 0,

"DSP_PERIPHERAL_L4EMU",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_DMM, L3_PERIPHERAL_DMM, SZ_1M, 0, 0,

"DSP_PERIPHERAL_DMM",

},

{

TYPE_DEVMEM, DSP_CMEM_IOBUFS, PHYS_CMEM_IOBUFS, DSP_CMEM_IOBUFS_SIZE, 0,

0, "DSP_CMEM_IOBUFS",

},

{

TYPE_DEVMEM, DSP_PERIPHERAL_EDMA, L3_PERIPHERAL_EDMA, SZ_1M*3, 0,

0, "DSP_EDMA",

},

{

TYPE_DEVMEM, DSP_PCIE_SS1_CONFIG_REG_BASE, L3_PCIE_SS1_CONFIG_REG_BASE, SZ_8M, 0,

0, "DSP_PCIE_REG_BASE",

},

{

TYPE_DEVMEM, DSP_PCIE_SS1_CONFIG_SPACE_BASE, L3_PCIE_SS1_CONFIG_SPACE_BASE, SZ_256M, 0,

0, "DSP_PCIE_CONFIG_BASE",

},

};

#endif /* _RSC_TABLE_DSP_H_ */

device_tree_file

------cut here-----------------

reserved-memory {

#address-cells = <2>;

#size-cells = <2>;

ranges;

ipu1_memory_region: ipu1-memory@9f000000 {

compatible = "shared-dma-pool";

reg = <0x0 0x9f000000 0x0 0x0080000>;

reusable;

status = "disabled";

};

dsp1_memory_region: dsp1-memory@91000000 {

compatible = "shared-dma-pool";

reg = <0x0 0x91000000 0x0 0xE000000>;

reusable;

status = "okay";

};

ipu2_memory_region: ipu2-memory@90800000 {

compatible = "shared-dma-pool";

reg = <0x0 0x90800000 0x0 0x0080000>;

reusable;

status = "disabled";

};

dsp2_memory_region: dsp2-memory@9f800000 {

compatible = "shared-dma-pool";

reg = <0x0 0x9f800000 0x0 0xE000000>;

reusable;

status = "okay";

// phandle = <0x121>;

};

cmem_block_mem_0: cmem_block_mem@c0000000 {

reg = <0x0 0xc0000000 0x0 0x18000000>;

no-map;

status = "okay";

};

};

cmem {

compatible = "ti,cmem";

#address-cells = <1>;

#size-cells = <0>;

#pool-size-cells = <2>;

status = "okay";

cmem_block_0: cmem_block@0 {

reg = <0>;

memory-region = <&cmem_block_mem_0>;

cmem-buf-pools = <1 0x0 0x18000000>;

};

};

------cut here-----------------

Thanks,

Shashank