Other Parts Discussed in Thread: SYSBIOS

Tool/software:

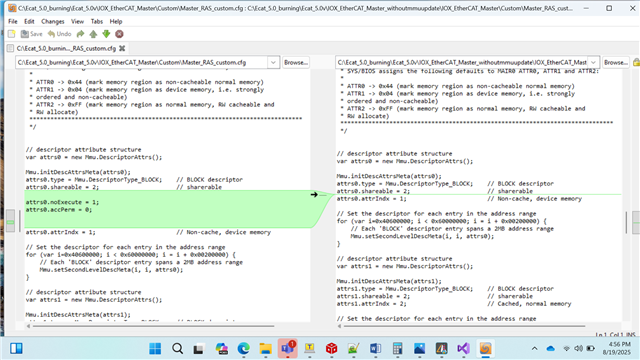

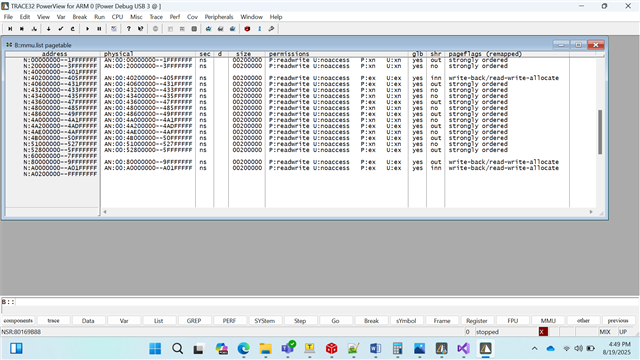

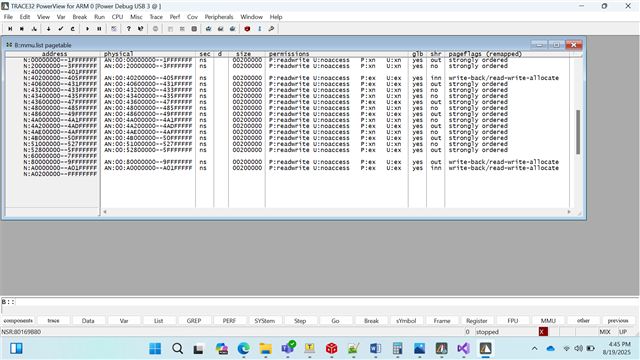

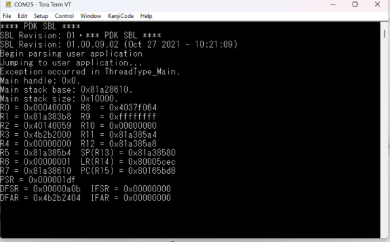

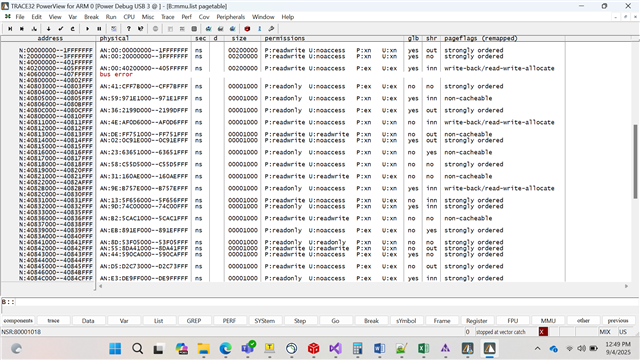

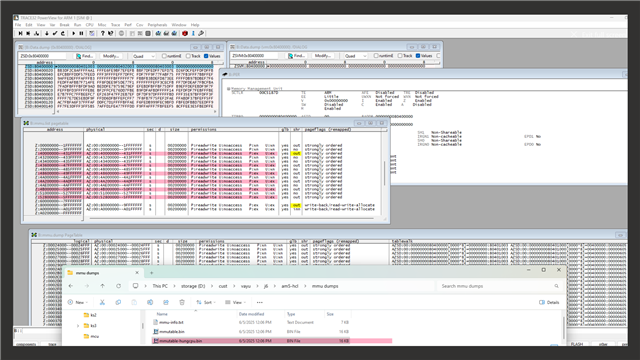

1. we have hug issue with pipeline stall, on review TI suggested to few changes in MMU table as highlighted in image , please help us in changing MMU configurations in SYSBIOS .cfg and help in understanding attr0 .. and MARI0 etc.

system details

we are using only one core A15_0

We have only 512MB DDR

we have Shared GPMC SRAM with FPGA.

we are PCIe RC with inbound configuration.

.cfg for MMU configuration.

/***********************************************

* MMU Configuration *

***********************************************/

var Mmu = xdc.useModule('ti.sysbios.family.arm.a15.Mmu');

Mmu.enableMMU = true;

/******************************************************************************

*

* SYS/BIOS assigns the following defaults to MAIR0 ATTR0, ATTR1 and ATTR2:

*

* ATTR0 -> 0x44 (mark memory region as non-cacheable normal memory)

* ATTR1 -> 0x04 (mark memory region as device memory, i.e. strongly

* ordered and non-cacheable)

* ATTR2 -> 0xFF (mark memory region as normal memory, RW cacheable and

* RW allocate)

******************************************************************************

*/

// descriptor attribute structure

var attrs0 = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(attrs0);

attrs0.type = Mmu.DescriptorType_BLOCK; // BLOCK descriptor

attrs0.shareable = 2; // sharerable

attrs0.attrIndx = 1; // Non-cache, device memory

// Set the descriptor for each entry in the address range

for (var i=0x40600000; i < 0x60000000; i = i + 0x00200000) {

// Each 'BLOCK' descriptor entry spans a 2MB address range

Mmu.setSecondLevelDescMeta(i, i, attrs0);

}

// descriptor attribute structure

var attrs1 = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(attrs1);

attrs1.type = Mmu.DescriptorType_BLOCK; // BLOCK descriptor

attrs1.shareable = 2; // sharerable

attrs1.attrIndx = 2; // Cached, normal memory

// Set the descriptor for each entry in the address range

for (var i=0x80000000; i < 0xA0000000; i = i + 0x00200000) {

// Each 'BLOCK' descriptor entry spans a 2MB address range

Mmu.setSecondLevelDescMeta(i, i, attrs1);

}

// descriptor attribute structure

var peripheralAttrs = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(peripheralAttrs);

peripheralAttrs.type = Mmu.DescriptorType_BLOCK; // BLOCK descriptor

peripheralAttrs.noExecute = true; // not executable

peripheralAttrs.accPerm = 0; // read/write at PL1

peripheralAttrs.attrIndx = 1; // MAIR0 Byte1 describes

// memory attributes for

// each BLOCK MMU entry

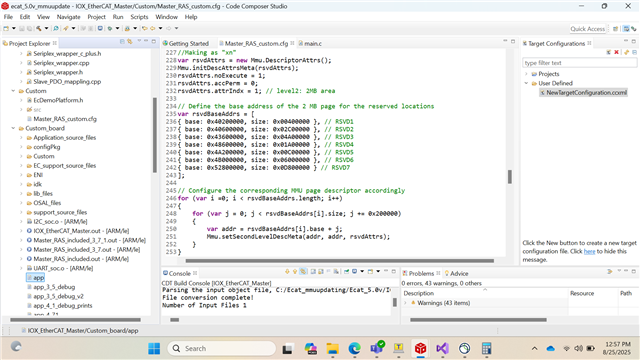

// Define the base address of the 2 MB page

// the peripheral resides in.

var peripheralBaseAddrs = [

{ base: 0x4ae00000, size: 0x00100000 }, // PRM

{ base: 0x51000000, size: 0x00800000 }, // pcie_ss1 regs

{ base: 0x51800000, size: 0x01000000 }, // pcie_ss2 regs

{ base: 0x20000000, size: 0x10000000 }, // pcie_ss1 data

{ base: 0x30000000, size: 0x10000000 }, // pcie_ss2 data

/* Following registers for IODELAY/PINMUX */

{ base: 0x4844a000, size: 0x00001000 },

{ base: 0x48447000, size: 0x00001000 },

{ base: 0x4a002000, size: 0x00001000 },

{ base: 0x43300000, size: 0x00300000 }

];

// Configure the corresponding MMU page descriptor accordingly

for (var i =0; i < peripheralBaseAddrs.length; i++)

{

for (var j = 0; j < peripheralBaseAddrs[i].size; j += 0x200000)

{

var addr = peripheralBaseAddrs[i].base + j;

Mmu.setSecondLevelDescMeta(addr, addr, peripheralAttrs);

}

}

//GPMC

var attrs = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(attrs);

attrs.type = Mmu.DescriptorType_BLOCK;

attrs.noExecute = true;

attrs.accPerm = 0; // R/W at PL1

attrs.attrIndx = 4; // Use MAIR0 Byte2

Mmu.setMAIRMeta(4, 0x04);

Mmu.setSecondLevelDescMeta(0x43200000, 0x43200000, attrs);

/* Set IO Delay configuration areas as non-cache */

attrs.attrIndx = 1;

Mmu.setSecondLevelDescMeta(0x4844a000, 0x4844a000, attrs);

Mmu.setSecondLevelDescMeta(0x4ae07d00, 0x4ae07d00, attrs);

var attrs = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(attrs);

attrs.type = Mmu.DescriptorType_BLOCK;

attrs.shareable = 2; // sharerable

attrs.attrIndx = 1; // Non-cache, device memory

Mmu.setSecondLevelDescMeta(0x50000000, 0x50000000, attrs); // this covers the first 2MB

Mmu.setSecondLevelDescMeta(0x50200000, 0x50200000, attrs);

// descriptor attribute structure

var peripheralAttrs = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(peripheralAttrs);

peripheralAttrs.type = Mmu.DescriptorType_TABLE;

Mmu.setFirstLevelDescMeta(0, 0, peripheralAttrs);

peripheralAttrs.type = Mmu.DescriptorType_BLOCK; // BLOCK descriptor

peripheralAttrs.noExecute = true; // not executable

peripheralAttrs.accPerm = 0; // read/write at PL1

peripheralAttrs.attrIndx = 4; // Non-cache, device memory

// MAIR0 Byte1 describes

// memory attributes for

// each BLOCK MMU entry

// write memory region attribute in mairRegAttr[2] i.e. MAIR0 Reg Byte2

Mmu.setMAIRMeta(4, 0x00);

var gpmcAttrs = new Mmu.DescriptorAttrs();

Mmu.initDescAttrsMeta(gpmcAttrs);

gpmcAttrs.type = Mmu.DescriptorType_BLOCK;

gpmcAttrs.shareable = 2;

gpmcAttrs.noExecute = 1;

gpmcAttrs.accPerm = 0;

gpmcAttrs.attrIndx = 1; // level2: 2MB area (level1 is 1GB area)

/* Configure the corresponding MMU page descriptor accordingly *//* For AM572x GPMC */

for (var gpmcBaseAddr = 0x00000000; gpmcBaseAddr < 0x20000000; gpmcBaseAddr += 0x200000)

{

Mmu.setSecondLevelDescMeta(gpmcBaseAddr,gpmcBaseAddr,gpmcAttrs);

}