Tool/software:

Dear Team,

We are using AM6442BSDGHAALV in one of our design and we are calculating the ZTarget for VDD_CORE using the below formula

Ztarget = (Voltage Rail x %Ripple) / 0.5 x Imax

Voltage Rail = 0.75V

%Ripple = 1.6%

Imax = 2A

%Ripple = 1.6% had arrived based on the below methodology.

1) We are using the PMIC: TPS6522053RHBR whose BUCK-1 Minimum output voltage is 0.73875V (0.75V Typical). Considering the ripple of -1.5% as the worst-case scenario.

2) We are using the Processor: AM6442BSDGHAALV whose Minimum Input Voltage of VDD_CORE (0.75V Typical) is 0.715V. whose minimum ripple is calculated to be -4.66667%.

3) Now ripple margin is calculated to be (-4.66667) - (-1.5) = -3.16667%

4) Furthermore -3.16667 is divided by 2 to have a stringent Ztarget for VDD_CORE i,e.: (-3.16667 / 2) = 1.58333% rounding off as 1.6%.

Now while substituting the above values to the Ztarget formula, we get:

Ztarget = (0.75V x 1.6%) / (0.5 x 2A) = 12mΩ.

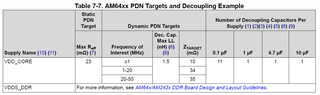

But when we refer the TI document "SPRAC76G – NOVEMBER 2022 – REVISED FEBRUARY 2024" (Sitara Processor Power Distribution Networks: Implementation and Analysis) in Table 7-7 we see the different Ztarget values, below is the snapshot of the same for your reference.

Can you please explain us how did TI arrive to the different Ztarget values as given below?

10mΩ for ≤1MHz

34mΩ for 1-20 MHz

35mΩ for 20-50MHz

For arriving to the above values, was the input voltage to VDD_CORE considered as an Ideal Voltage as 0.75V?

Thank you.

Regards

Amarnath G