Tool/software:

Hello there,

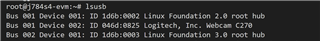

we want to bring up USB Camer on custom Linux with J784S4XEVM board.

could you please share the steps to do it or documentation where things are given ?

with TI documentation the build is thru Yocto Linux we want to do the bring up directly on the booted board with existing kernel

thanks and kind regards

Mohan