Part Number: TDA4AL-Q1

Tool/software:

Hello Team,

We are using TDA4AL-Q1 processor in one of our design & would like to do Signal Integrity simulation for LPDDR4 interface with 4266MT/ps data rate.

So, we need timing specification values for the below mentioned parameters for TDA4AL processor. Currently, TDA4AL datasheet doesn't have timing specifications for LPDDR4 interface.

Output timing Parameters:

- tCKCA, tCKCS, tCKCKE : CA, CS, CKE prelaunch delay relative to CK (both min & max values)

- tDQSDQ: DQ/DM prelaunch delay relative to CK (both min & max values)

- tCKDQS: DQS delay relative to CK

Input timing Parameters:

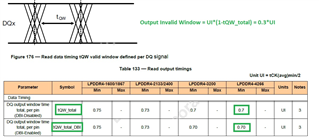

- VdIVW(mV), TdIVW1(UI), TdIVW2(UI): Data Read eye masks parameters values(min).

- TdiPW(UI): Minimum Read Data Oulse Width

- VIHL_AC_DQ(mV): addition to eye mask if any additional requirement for the signal to reach a minimum peal level.

Please do the needful ASAP.

Best Regards,

Hoysalachar N N