Part Number: PROCESSOR-SDK-AM64X

Other Parts Discussed in Thread: TMDS64EVM

Tool/software:

Hi,

I am running TMDS64EVM board. I am in SBL stage, there is no OS.

I am initializing ddr.

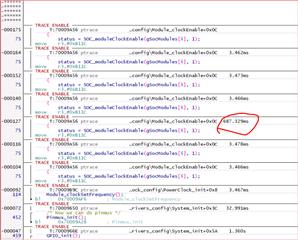

I found during the whole boot process, "ddr enable clock" takes 700ms.

question. is this timing reasonable, is there a way to bypass?

Why it takes that long to enable ddr clock. I mean the whole boot process, maybe < 1 second? Enable that ddr clock takes 60% of time.

Thanks