[continue conversation from https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1529704/am620-q1-failed-to-use-mcu-only-mode]

Hi, Gibbs,

We have solved the problem that mcu cannot control IO in only mode.

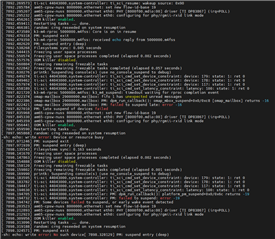

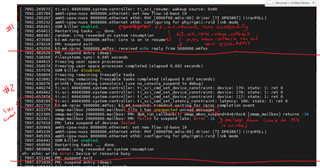

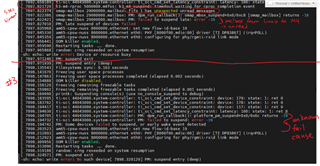

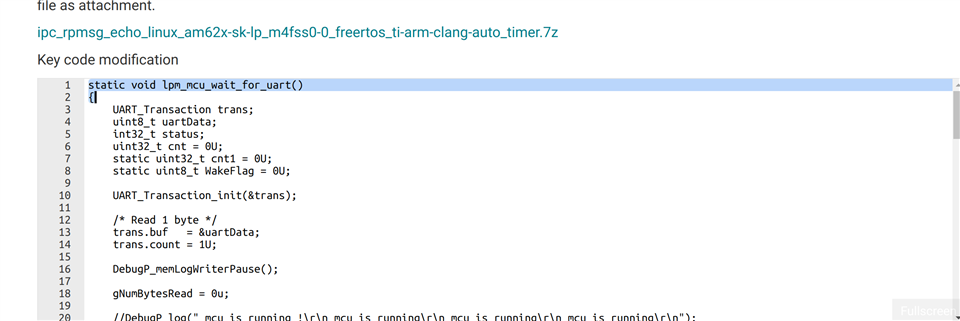

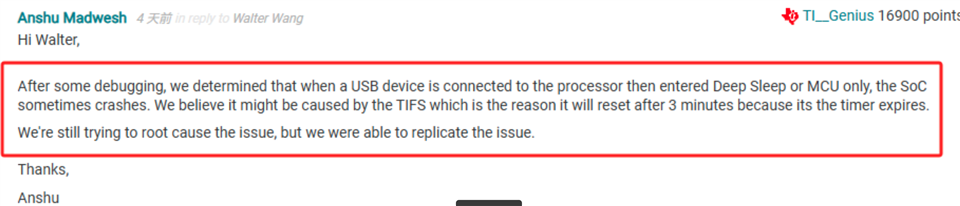

Next, please give priority to the problem that mcu wakes up soc and causes IPC crash and automatic restart

Thanks