Tool/software:

We are using an FPGA chip connected to the MIPI CSI2 clock lane and 4 data lanes of an AM625. The FPGA starts sending MIPI data immediately after loading the bitstream, with the format being 640x480, YVYU8_1X16 (data type 0x1e) and a link frequency of 400MHz. After Linux boots, we load the imx459 driver, which includes some code for configuring the ov5640 for testing on an AM62B-P1 motherboard with a camera. Testing uses the same resolution and format, and MIPI data can be obtained normally in this configuration.

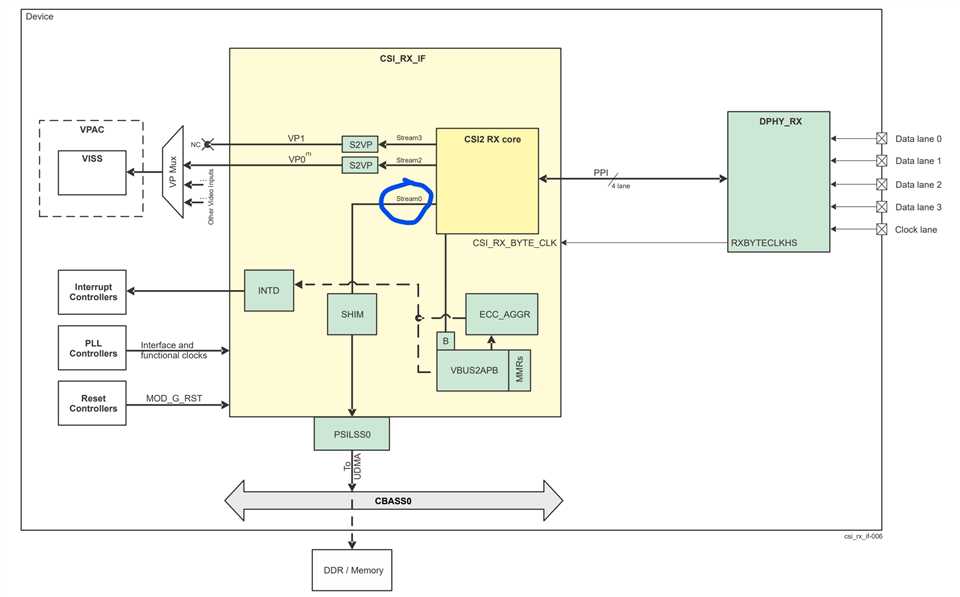

When the driver is ported to our project motherboard, it can successfully create v4l-dev, videoX, and mediaX devices without reporting any errors, but MIPI data cannot be obtained. The topology is as follows:

Media controller API version 6.6.58 Media device information ------------------------ driver j721e-csi2rx model TI-CSI2RX serial bus info platform:30102000.ticsi2rx hw revision 0x1 driver version 6.6.58 Device topology - entity 1: 30102000.ticsi2rx (5 pads, 5 links, 1 route) type V4L2 subdev subtype Unknown flags 0 device node name /dev/v4l-subdev0 routes: 0/0 -> 1/0 [ACTIVE] pad0: Sink [stream:0 fmt:YVYU8_1X16/640x480 field:none colorspace:srgb xfer:srgb ycbcr:601 quantization:lim-range] <- "cdns_csi2rx.30101000.csi-bridge":1 [ENABLED,IMMUTABLE] pad1: Source [stream:0 fmt:YVYU8_1X16/640x480 field:none colorspace:srgb xfer:srgb ycbcr:601 quantization:lim-range] -> "30102000.ticsi2rx context 0":0 [ENABLED,IMMUTABLE] pad2: Source -> "30102000.ticsi2rx context 1":0 [ENABLED,IMMUTABLE] pad3: Source -> "30102000.ticsi2rx context 2":0 [ENABLED,IMMUTABLE] pad4: Source -> "30102000.ticsi2rx context 3":0 [ENABLED,IMMUTABLE] - entity 7: cdns_csi2rx.30101000.csi-bridge (5 pads, 2 links, 1 route) type V4L2 subdev subtype Unknown flags 0 device node name /dev/v4l-subdev1 routes: 0/0 -> 1/0 [ACTIVE] pad0: Sink [stream:0 fmt:YVYU8_1X16/640x480 field:none colorspace:srgb xfer:srgb ycbcr:601 quantization:lim-range] <- "imx459 spi1.0":0 [ENABLED,IMMUTABLE] pad1: Source [stream:0 fmt:YVYU8_1X16/640x480 field:none colorspace:srgb xfer:srgb ycbcr:601 quantization:lim-range] -> "30102000.ticsi2rx":0 [ENABLED,IMMUTABLE] pad2: Source pad3: Source pad4: Source - entity 13: imx459 spi1.0 (1 pad, 1 link, 0 routes) type V4L2 subdev subtype Sensor flags 0 device node name /dev/v4l-subdev2 pad0: Source [stream:0 fmt:Y8_1X8/640x480 field:none colorspace:raw xfer:none ycbcr:601 quantization:full-range] -> "cdns_csi2rx.30101000.csi-bridge":0 [ENABLED,IMMUTABLE] - entity 19: 30102000.ticsi2rx context 0 (1 pad, 1 link) type Node subtype V4L flags 0 device node name /dev/video0 pad0: Sink <- "30102000.ticsi2rx":1 [ENABLED,IMMUTABLE] - entity 25: 30102000.ticsi2rx context 1 (1 pad, 1 link) type Node subtype V4L flags 0 device node name /dev/video1 pad0: Sink <- "30102000.ticsi2rx":2 [ENABLED,IMMUTABLE] - entity 31: 30102000.ticsi2rx context 2 (1 pad, 1 link) type Node subtype V4L flags 0 device node name /dev/video2 pad0: Sink <- "30102000.ticsi2rx":3 [ENABLED,IMMUTABLE] - entity 37: 30102000.ticsi2rx context 3 (1 pad, 1 link) type Node subtype V4L flags 0 device node name /dev/video3 pad0: Sink <- "30102000.ticsi2rx":4 [ENABLED,IMMUTABLE]

The following commands are used for testing

v4l2-ctl --verbose -d /dev/video0 --set-fmt-video=width=640,height=480,pixelformat=YVYU --stream-mmap=2 --stream-poll

Test results:

VIDIOC_QUERYCAP: ok VIDIOC_G_FMT: ok VIDIOC_S_FMT: ok Format Video Capture: Width/Height : 640/480 Pixel Format : 'YVYU' (YVYU 4:2:2) Field : None Bytes per Line : 1280 Size Image : 614400 Colorspace : sRGB Transfer Function : sRGB YCbCr/HSV Encoding: ITU-R 601 Quantization : Limited Range Flags : VIDIOC_REQBUFS returned 0 (Success) VIDIOC_QUERYBUF returned 0 (Success) VIDIOC_QUERYBUF returned 0 (Success) VIDIOC_G_FMT returned 0 (Success) VIDIOC_QBUF returned 0 (Success) VIDIOC_QBUF returned 0 (Success) VIDIOC_STREAMON returned 0 (Success) select timeout

Kernel register settings of enabling the stream:

[ 28.709864] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:322] write reg: 0x10, value: 0x1 [ 28.709870] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:325] read back: 0x10, value: 0xf01 [ 28.709875] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:322] write reg: 0x20, value: 0x8c00001e [ 28.709880] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:325] read back: 0x20, value: 0x8c00001e [ 28.709885] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:322] write reg: 0x24, value: 0x0 [ 28.709890] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:325] read back: 0x24, value: 0x0 [ 28.709899] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:850] sizeimage: 614400 [ 28.709931] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:850] sizeimage: 614400 [ 28.709966] j721e-csi2rx 30102000.ticsi2rx: enable streams 1:0x1 [ 28.709974] j721e-csi2rx 30102000.ticsi2rx: Enabling all streams (1) on sink. [ 28.709993] j721e-csi2rx 30102000.ticsi2rx: enable streams 1:0x1 [ 28.710000] cdns-csi2rx 30101000.csi-bridge: enable streams [ 28.710071] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x4, value: 0x3 [ 28.710078] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x4, value: 0x0 [ 28.710083] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x100, value: 0x10 [ 28.710088] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x100, value: 0x0 [ 28.710093] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x200, value: 0x10 [ 28.710098] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x200, value: 0x0 [ 28.710144] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x300, value: 0x10 [ 28.710150] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x300, value: 0x0 [ 28.710155] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x400, value: 0x10 [ 28.710159] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x400, value: 0x0 [ 28.710207] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x4, value: 0x0 [ 28.710215] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x4, value: 0x0 [ 28.710221] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x100, value: 0x0 [ 28.710226] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x100, value: 0x0 [ 28.710231] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x200, value: 0x0 [ 28.710235] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x200, value: 0x0 [ 28.710240] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x300, value: 0x0 [ 28.710245] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x300, value: 0x0 [ 28.710249] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x400, value: 0x0 [ 28.710254] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x400, value: 0x0 [ 28.710263] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x8, value: 0x43210400 [ 28.710268] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x8, value: 0x43210400 [ 28.710286] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x40, value: 0x1f01f [ 28.710291] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x40, value: 0x1f01f [ 28.710316] MIPI D-PHY: pixelclocl: 0, bpp: 0, lanes: 4, hs_clk_rate 750000000, ui: 1334 [ 28.710381] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0x20, value: 0x429 [ 28.710387] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0x20, value: 0x429 [ 28.710417] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0x1000, value: 0x800000 [ 28.710422] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0x1000, value: 0x800000 [ 28.710437] hs_clk_rate = 750000000, rate = 1500 [ 28.710448] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0xb00, value: 0x273 [ 28.710453] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0xb00, value: 0x273 [ 28.710460] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0xb08, value: 0xaaaaaaaa [ 28.710465] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0xb08, value: 0xaaaaaaaa [ 28.710470] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0xb0c, value: 0xaa [ 28.710475] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0xb0c, value: 0xaa [ 28.710787] [drivers/phy/cadence/cdns-dphy-rx.c:163] wait 0xc10 bit 0, ret: 0 [ 28.710797] [drivers/phy/cadence/cdns-dphy-rx.c:170] wait 0xc14 bit 0 lane 0, ret: 0 [ 28.710803] [drivers/phy/cadence/cdns-dphy-rx.c:170] wait 0xc20 bit 0 lane 1, ret: 0 [ 28.710809] [drivers/phy/cadence/cdns-dphy-rx.c:170] wait 0xc30 bit 0 lane 2, ret: 0 [ 28.710815] [drivers/phy/cadence/cdns-dphy-rx.c:170] wait 0xc3c bit 0 lane 3, ret: 0 [ 28.710892] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x10c, value: 0x100 [ 28.710898] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x10c, value: 0x100 [ 28.710903] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x108, value: 0x0 [ 28.710908] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x108, value: 0x0 [ 28.710913] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x100, value: 0x1 [ 28.710917] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x100, value: 0x1 [ 28.710923] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x20c, value: 0x100 [ 28.710928] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x20c, value: 0x100 [ 28.710932] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x208, value: 0x0 [ 28.710937] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x208, value: 0x0 [ 28.710941] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x200, value: 0x1 [ 28.710946] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x200, value: 0x0 [ 28.711001] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x30c, value: 0x100 [ 28.711007] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x30c, value: 0x100 [ 28.711012] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x308, value: 0x0 [ 28.711017] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x308, value: 0x0 [ 28.711022] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x300, value: 0x1 [ 28.711026] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x300, value: 0x1 [ 28.711031] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x40c, value: 0x100 [ 28.711036] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x40c, value: 0x100 [ 28.711041] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x408, value: 0x0 [ 28.711045] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x408, value: 0x0 [ 28.711050] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x400, value: 0x1 [ 28.711055] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x400, value: 0x1

Kernel registers settings of stopping the stream:

[ 30.715046] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:322] write reg: 0x10, value: 0x0 [ 30.715118] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:325] read back: 0x10, value: 0xf00 [ 30.715133] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:322] write reg: 0x20, value: 0x0 [ 30.715138] [drivers/media/platform/ti/j721e-csi2rx/j721e-csi2rx.c:325] read back: 0x20, value: 0x0 [ 30.715243] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x100, value: 0x2 [ 30.715250] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x100, value: 0x2 [ 30.715256] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x200, value: 0x2 [ 30.715261] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x200, value: 0x0 [ 30.715316] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x300, value: 0x2 [ 30.715321] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x300, value: 0x2 [ 30.715327] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x400, value: 0x2 [ 30.715332] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x400, value: 0x2 [ 30.715427] [drivers/media/platform/cadence/cdns-csi2rx.c:149] write reg: 0x40, value: 0x0 [ 30.715432] [drivers/media/platform/cadence/cdns-csi2rx.c:152] read back: 0x40, value: 0x0 [ 30.715439] [drivers/phy/cadence/cdns-dphy-rx.c:81] write reg: 0x20, value: 0x0 [ 30.715445] [drivers/phy/cadence/cdns-dphy-rx.c:84] read back: 0x20, value: 0x0

Currently observed issue:

After writing start/stop commands to

After writing start/stop commands to

stream1_ctrl, the status read back does not indicate the start/stop state change.Status register values during operation:

dphy status : 0x333306d dphy error status : 0x0 integration debug : 0x10000000 error debug : 0x0 stream0 status : 0x80000111 stream1 status : 0x80000011 stream2 status : 0x80000111 stream3 status : 0x80000111