Tool/software:

Dear Champs,

Is it possible to achieve 24Mbps baudrate in PRUSS_UART?

or, it is possible to implement SW UART in PRUSS to achieve 24Mbps baudrate?

Thanks and Best Regards,

SI.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Dear Champs,

Is it possible to achieve 24Mbps baudrate in PRUSS_UART?

or, it is possible to implement SW UART in PRUSS to achieve 24Mbps baudrate?

Thanks and Best Regards,

SI.

Hello Sung-IL,

Hardware UART

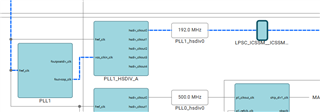

The input clock to the hardware UART peripheral is 192MHz according to the AM62x clock tree tool:

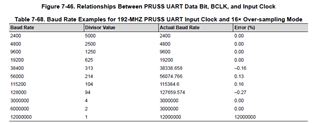

So if there was an 8x oversampling mode, then 24MHz would be possible (192MHz / 8). However, the PRU hardware only allows for 16x oversampling, or 13x oversampling. Thus the hardware UART peripheral in the PRU subsystem only supports up to 12MHz baudrate.

From the AM62x Technical reference manual, PRU > PRUSS UART

7.4.7.2.4 PRUSS UART Clock Generation and Control

The PRUSS UART0 bit clock is derived from an input clock to the PRUSS UART0. See the device-specific

Datasheet to check the maximum data rate supported by the PRUSS UART0.

Figure 7-45 is a conceptual clock generation diagram for the PRUSS UART0. The processor clock generator

receives a signal from an external clock source and produces a PRUSS UART0 input clock with a programmed

frequency. The PRUSS UART0 contains a programmable baud generator that takes an input clock and divides

it by a divisor in the range between 1 and (216 - 1) to produce a baud clock (BCLK). The frequency of BCLK is

sixteen times (16×) the baud rate (each received or transmitted bit lasts 16 BCLK cycles) or thirteen times (13×)

the baud rate (each received or transmitted bit lasts 13 BCLK cycles). When the PRUSS UART0 is receiving,

the bit is sampled in the 8th BCLK cycle for 16× over sampling mode and on the 6th BCLK cycle for 13×

over-sampling mode. The 16× or 13× reference clock is selected by configuring the mode definition register:

UART_MODE[0] OSM_SEL bit. The formula to calculate the divisor is:

Divisor = UART input clock frequency [MODE.OSM_SEL = 0h]

-------------------------------------

Desired baud rate x 16

Divisor = UART input clock frequency [MODE.OSM_SEL = 1h]

-------------------------------------

Desired baud rate x 13

Software UART

The Software UART that was created for AM335x was only tested up to 115,200. But that was partially to enable each PRU core to implement up to 3 UART interfaces, for a total of 6 additional UARTs per PRU-ICSS. Documentation here: https://software-dl.ti.com/processor-sdk-linux/esd/docs/07_03_00_005/linux/Foundational_Components/PRU-ICSS/Linux_Drivers/pru-sw-uart.html

We are currently working on software UART implementation for some more recent PRU devices. I will check with the team to see what specs we are targeting. Feel free to ping the thread if I have not replied within a few business days.

Regards,

Nick

Hello Sung-IL,

I am still looking into our latest software UART implementations.

Is this a full duplex UART, or a half duplex UART application?

Regards,

Nick

Final followup on software UART with AM62x:

right now, the easiest software UART option for me to implement on the AM62x would be to port the AM335x software UART project to AM62x. That would allow us to add up to 6 additional UARTs running at up to 115,200 baud rate.

At some point, I would like to port the AM335x Linux driver and PRU firmware to AM62x, probably publishing in the upcoming open-pru repo. But I do not have that effort scheduled right now.

Regards,

Nick