What is the best way to interface the AM389x to another processor via Gigabit Ethernet? The other processor has GMII interface, can the 2 be connected directly via GMII to GMII? Or must there be Phys in between?

Charles

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

What is the best way to interface the AM389x to another processor via Gigabit Ethernet? The other processor has GMII interface, can the 2 be connected directly via GMII to GMII? Or must there be Phys in between?

Charles

Marc,

Thanks, I guess the real question is, if we are connecting the Gig E to another processor can you connect the GMII ports of each processor together? or do you need to go from

GMII to PHY --- then to the PHY to GMII of the next processor? These are both on the same board, so this is not going off board or across cards..Not sure if this is possible.. or would work.

Charles

Charles,

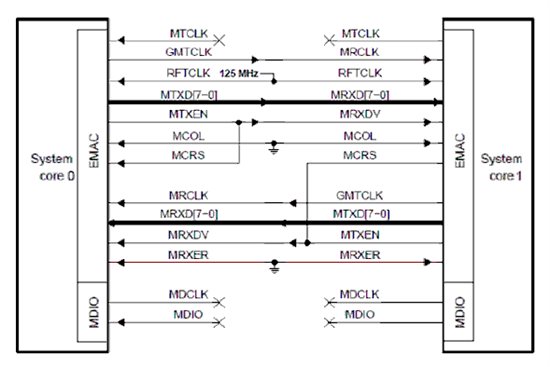

Thanks for the additional details - I was thinking that the connection would be outside of your system. In this case GMII can be cross connected (without using PHYs):

Hi Marc,

1) What about GMTCLK, RXCLK and TXCLK signals?

2) Could CRS be shorted to TXEN or it has to be tied LOW? I found TI's datasheet about direct connections in the document "Inter-DM6467 Communications Using Direct GMII Connections".

2480.Inter-DM6467 Communications Using Direct GMII Connections E2E .pdf

Regards,

Adam

There are other pins that may need to be addressed:

Here is my guess:

|

MPU 1 |

Direction |

MPU 2 |

Notes |

|

EMAC Module |

|

|

|

|

EMAC_TXCLK |

I |

2.5/25 MHz |

10/100 Common on both |

|

EMAC_GMTCLK |

O |

open |

1000 |

|

EMAC_TXD[0-7] |

O |

EMAC_RXD[0-7] |

Crossed data |

|

EMAC_TXEN |

O |

EMAC_RXDV |

|

|

EMAC_COL |

I (GND) |

GND |

Not sure of polarity |

|

EMAC_CRS |

I (GND) |

GND |

Not sure of polarity |

|

EMAC_RXCLK |

I |

2.5/25/125 MHz |

10/100/1000 Common on both |

|

EMAC_RXD[0-7] |

I |

EMAC_TXD[0-7] |

Crossed data |

|

EMAC_RXDV |

I |

EMAC_TXEN |

|

|

EMAC_RXER |

I (GND) |

GND |

Not sure of polarity |

|

|

|

|

|

|

MDIO module |

|

|

|

|

MDIO_MCLK |

O |

Unused |

Unsure |

|

MDIO_MDIO |

I/O |

Unused |

Unsure |

Ground all _COL, _CRS, RXER signals on both MPUs

Can you help resolve these questions:

1) Is the phy in the new AM389x equivalent to that used in the DM6467?

2) What are the details for using the EMACs for MCU to MCU Communication?

3) Does EMAC_CRS get tied to GND or does it tie to the same MCUs RXDV?

|

MPU 1 |

Direction |

MPU 2 |

Notes |

|

EMAC Module |

|

|

|

|

EMAC_TXCLK |

I |

Unused on both |

|

|

EMAC_GMTCLK |

O |

EMAC_RXCLK |

Cross Clocks |

|

EMAC_TXD[0-7] |

O |

EMAC_RXD[0-7] |

Crossed data |

|

EMAC_TXEN |

O |

EMAC_RXDV |

Cross ETn/RVa |

|

EMAC_COL |

I (GND) |

Ground Both |

|

|

EMAC_CRS |

I (???) |

GND or EMAC_RXDV_1 |

Please see attached diagram |

|

EMAC_RXCLK |

I |

EMAC_GMTCLK |

Cross Clocks |

|

EMAC_RXD[0-7] |

I |

EMAC_TXD[0-7] |

Crossed data |

|

EMAC_RXDV |

I |

EMAC_TXEN |

Cross ETn/RVa |

|

EMAC_RXER |

I (GND) |

Ground Both |

|

|

|

|

|

|

|

MDIO module |

|

|

|

|

MDIO_MCLK |

O |

Unused |

|

|

MDIO_MDIO |

I/O |

Unused |

Thanks,

Rinzai Bell