Tool/software:

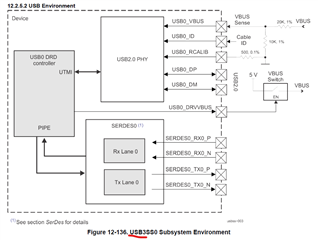

We are using a TDA4AEN8K5AAMWRQ1 and want to enable a USB3 SuperSpeed connection. In the trm (SPRUJB3B.pdf) the following is depicted:

This is exactly the current setup we use in our design. Now we see the dwc3 driver complains no superspeed support and in TI forums like here we see statements like:

USB0 only support USB2.0

USB1 + serdes0 is used to support USB3.0

Now we wonder if we need to change our design to fully support USB3 and make usage of the USB1_* pins instead.

If our and the depicted setup is correct and should work: How does the required dts setup for the &usbss0 and &usb0 nodes need to look like?

Thank you and

-Best regards, Götz-