Tool/software:

Dear TI Support Team,

I'm working with both the J721S2 and J721E EVM boards, and I'm experiencing issues with USB 3.x connectivity:

Boards and SDK Versions:

-

J721S2 using

rtos-j721s2-evm-10_01_00_04 -

J721E using

rtos-j721e-evm-10_01_00_04

Issues observed:

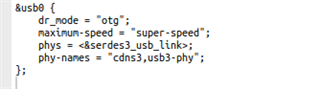

J721S2:

-

The USB Type-A port is not detected at all.

-

The USB Type-C port works, but it only connects USB devices at High-Speed (USB 2.0 / 480 Mbps).

-

I have tested multiple verified USB 3.0/3.1 flash drives and cables, all of which work correctly at 5 Gbps on a PC.

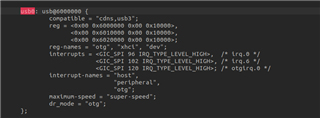

J721E:

-

Both the Type-A and Type-C ports are functional, but all USB 3.x devices are still limited to USB 2.0 speed (480 Mbps).

Other Checks:

-

The ports are labeled as USB 3.1 capable.

-

The flash drives and cables are confirmed to support USB 3.0/3.1.

-

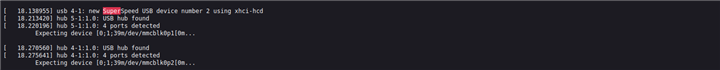

lsusb -talways shows480Mspeed regardless of port or board. -

dmesgconfirms that the host controllers support USB 3.0 (xhci-hcd, SuperSpeed capable). -

Still, devices are always negotiated as USB 2.0 (High-Speed).

Questions:

-

Is there any known limitation with RTOS SDK 10.01.00.04 that affects USB 3.x negotiation?

- Any debugging tips or recommended device connection paths to verify USB 3.x functionality?

Best regards,

Liu