Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

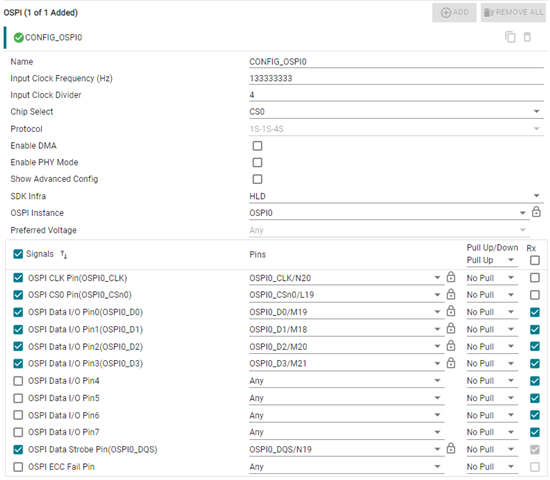

I tried to open Flash from the R5F0-0 core of AM6442, but the function Board_driversOpen did not complete successfully.

Please give me some advice on how to solve the problem.

Background

First, I used a debugger to find where the failure was occurring.

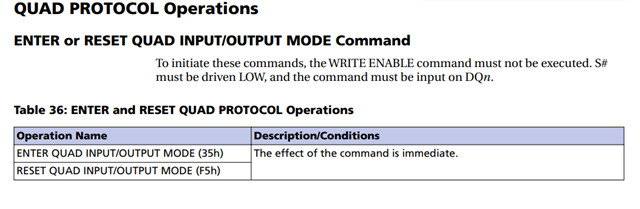

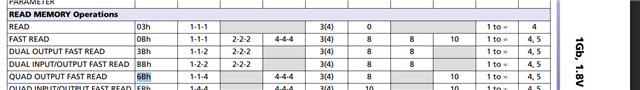

As a result, I found that Flash_norOspiCmdRead had failed on line 151 of flash_nor_ospi.c, and that the program was waiting for a timeout.

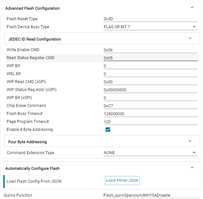

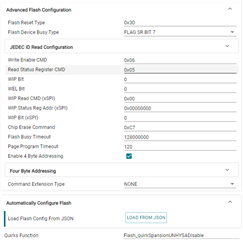

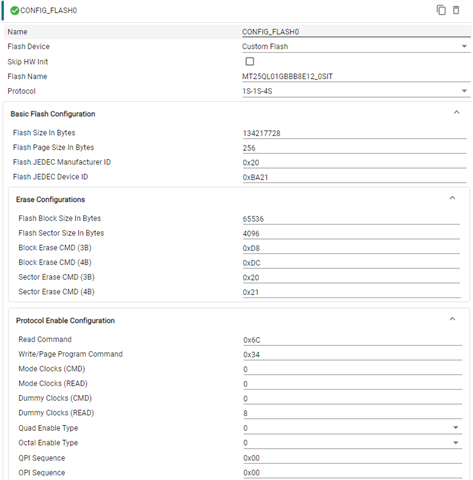

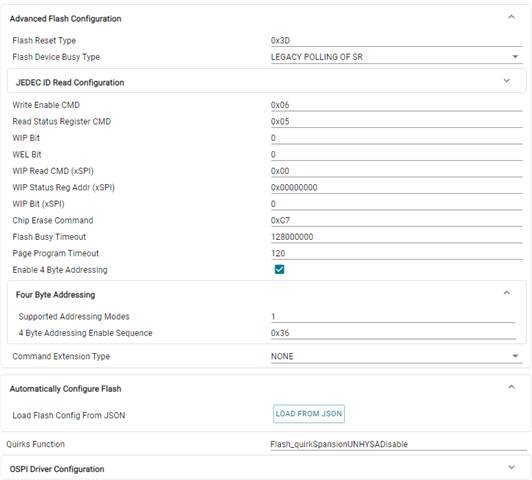

Checking Skip HW Init in the sysconfig settings resolved this non-terminating state.

However, it seemed that the flash open itself had failed, and the debug output from UART displayed "FLASH open failed for instance 0!!!".

After searching for where the failure was occurring, I found "status = SystemP_FAILURE" on line 901 of flash_nor_ospi.c.

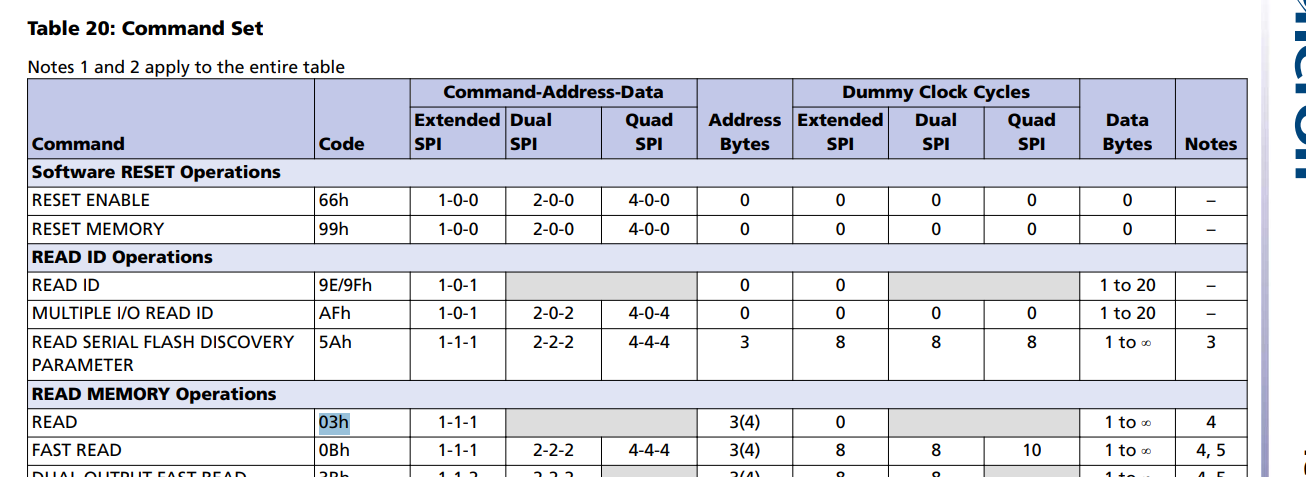

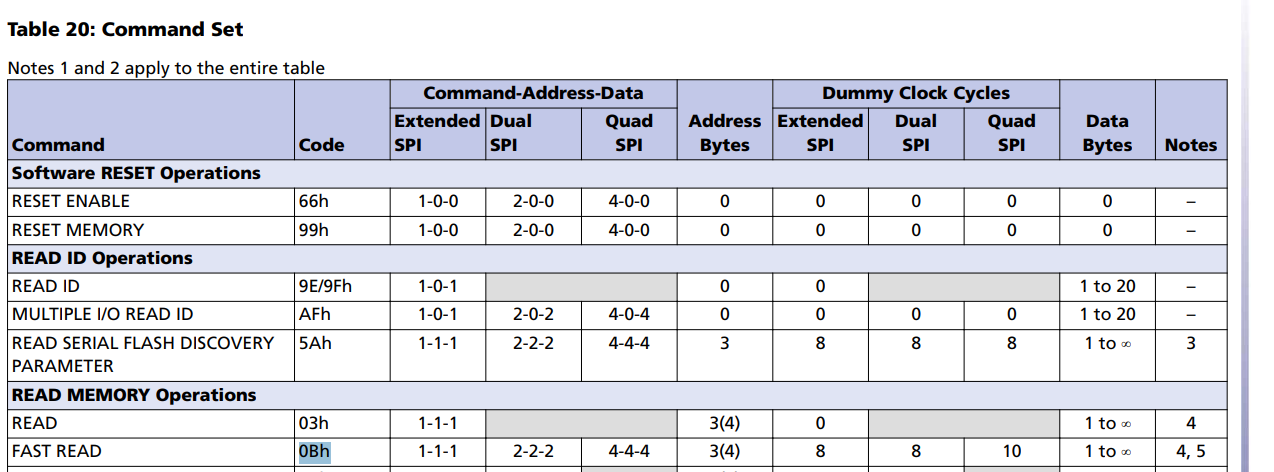

The failure occurred because the manufacturerId and deviceId read out were different from the values set in sysconfig.

The ID values read out were as follows: manufacturerId = 0xFF deviceId = oxFFFF

Notes

- Flash model number: MT25QL01GBBB8E12_0SIT (Micron)

- Uses an RTOS called "xxx".

- A development environment is used that matches the RTOS.

- Other functions such as GPIO and UART have been confirmed to work.