Tool/software:

Hello, TI team:

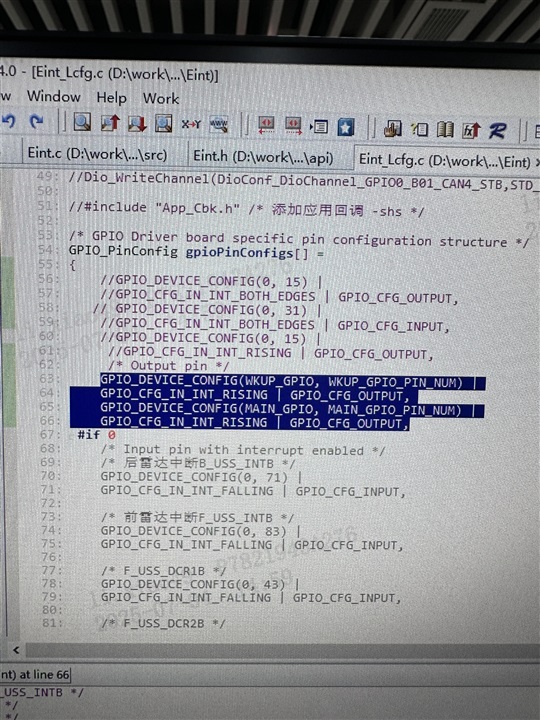

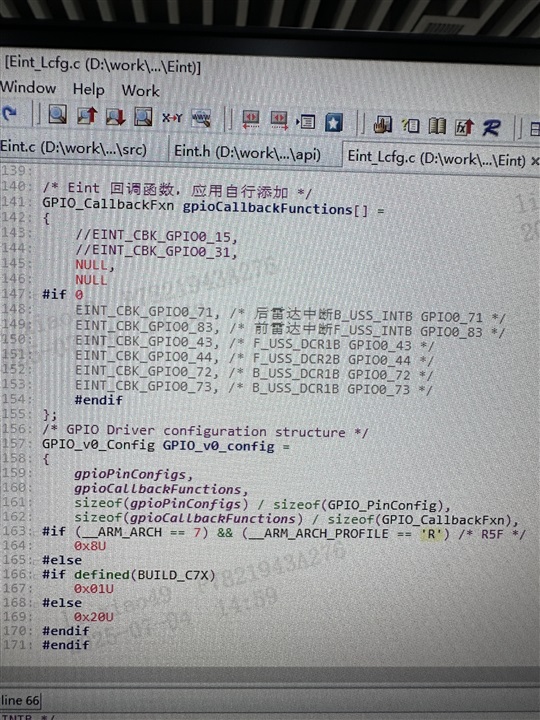

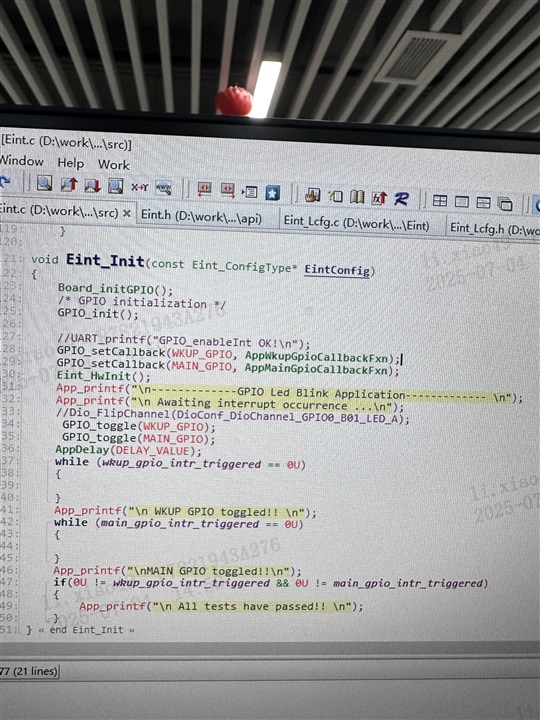

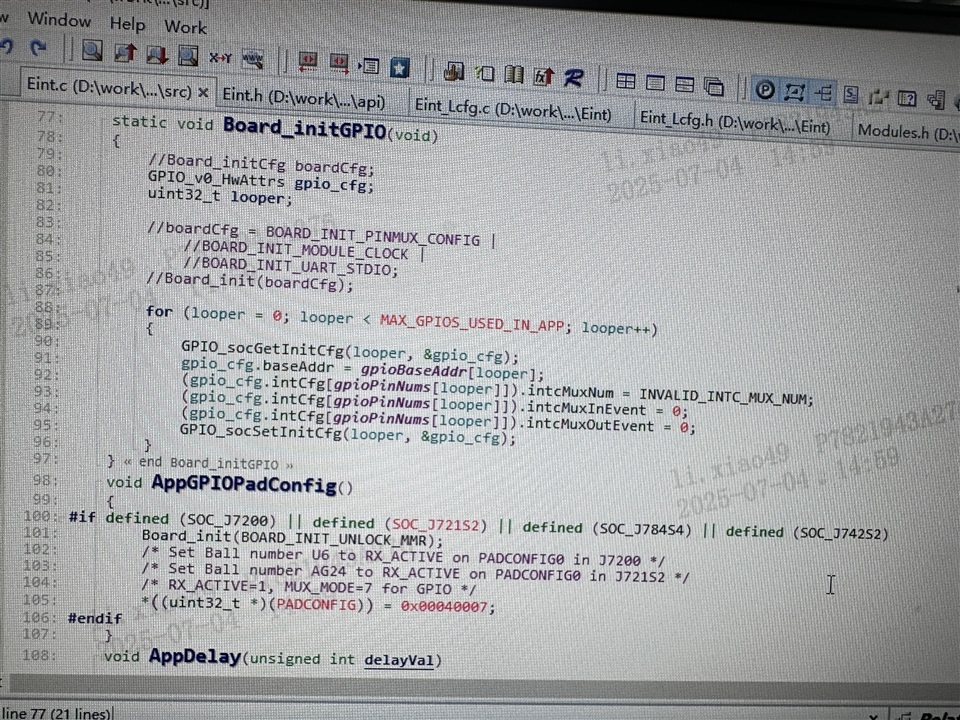

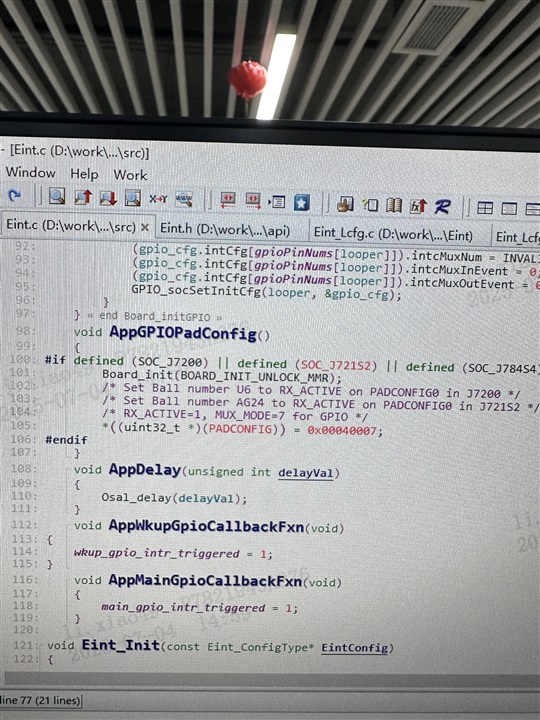

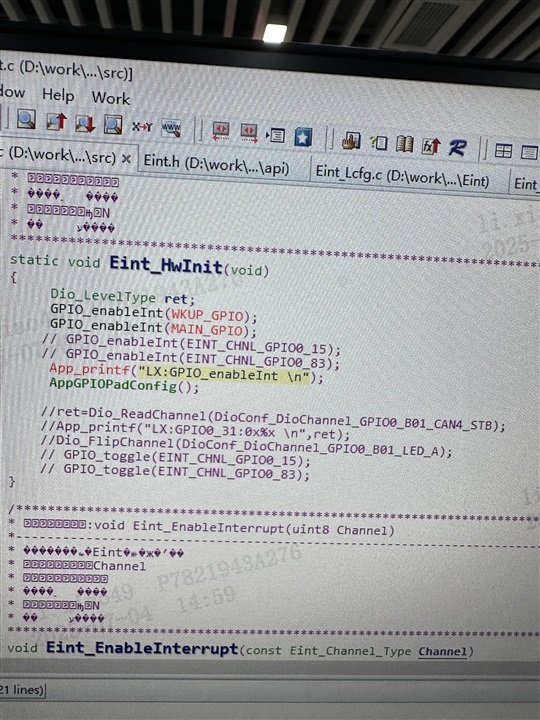

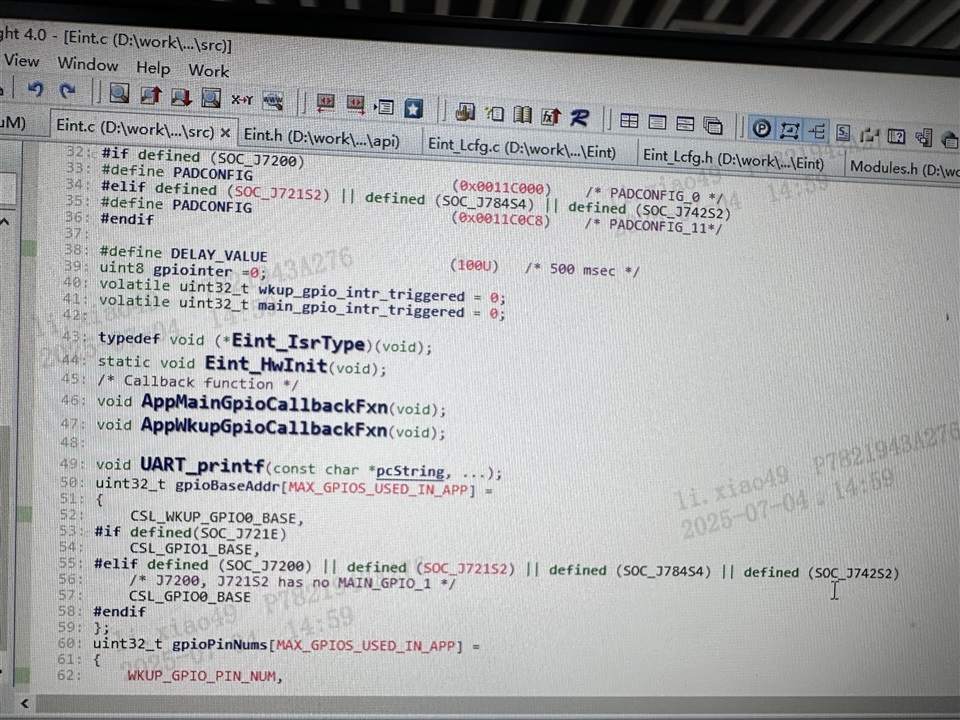

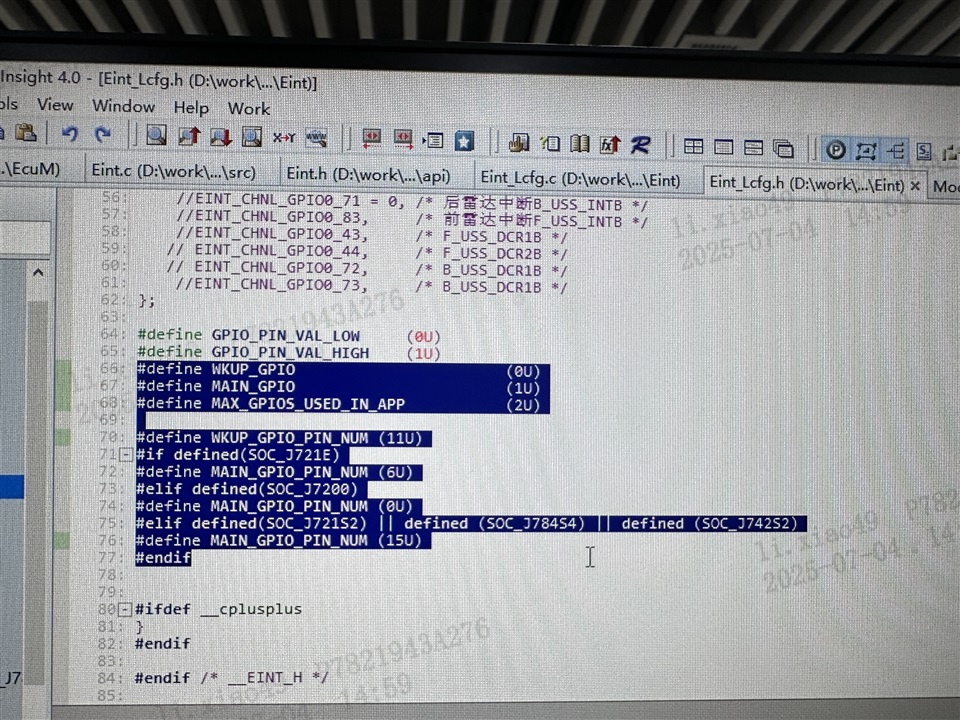

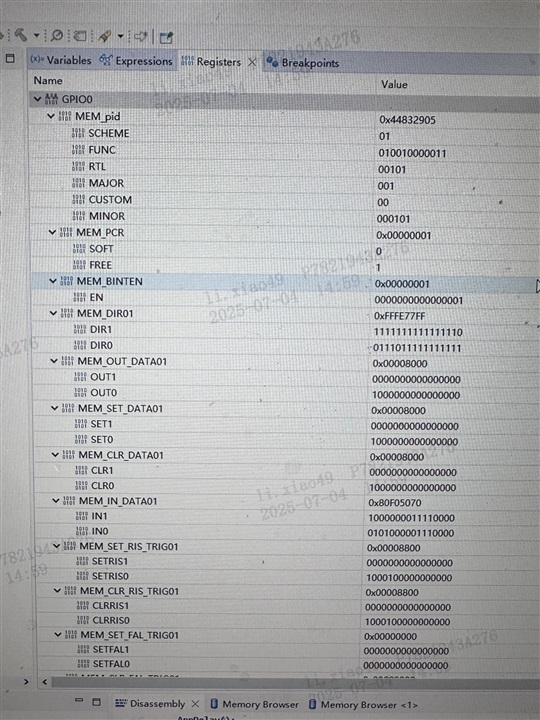

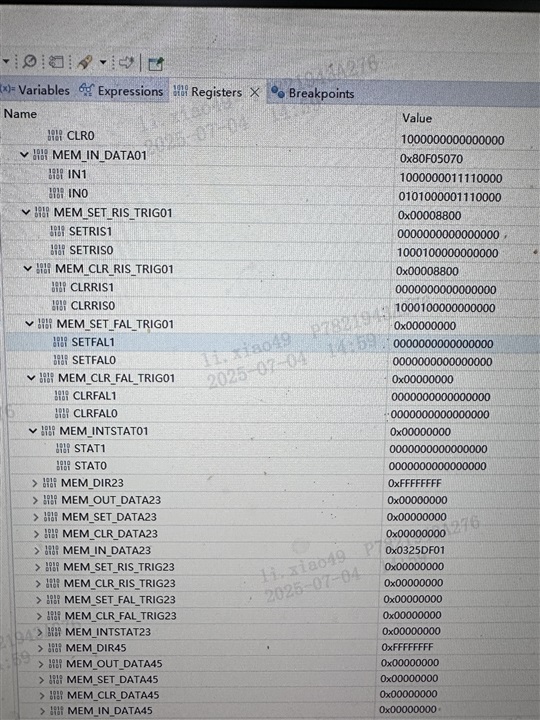

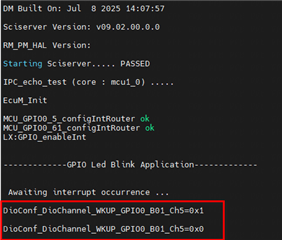

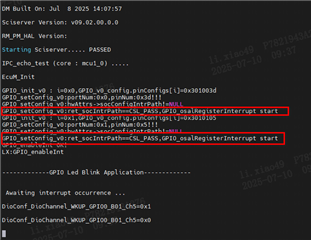

I found that the interrupt could not be triggered when using the interrupt trigger of GPIO, I refer to the code of the led_blink under the test folder of the gpio module in pdk10.0, I used the GPIO0_15 of the MAIN domain, set it as the output, call Board_initGPIO () first, then call GPIO_init(), then call GPIO_setCallback(), then call GPIO_enable(), When calling AppGPIOConfig() and then calling GPIO_toggle flipping the level so that an interrupt can be triggered, but the interrupt is not actually triggered, or even entering the GPIO_V0_hwiFxn(), the values of the BINTEN, DIR01, SET_DATA01, SET_RIS_TRIG01 registers of GPIO0 are the same as the settings, but the value of the corresponding bit of the INTSTAT01 is 0, indicating that no interrupt has occurred , the value of the specific register and the code I put below, please experts help me see as soon as possible, to achieve interrupt triggering, the project is urgent, and the trouble is as soon as possible.