Part Number: TDA4VE-Q1

Other Parts Discussed in Thread: TDA4VL, TDA4VM

Tool/software:

Hi TI expert,

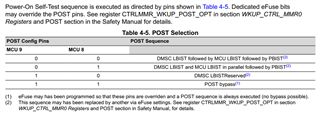

In our original hardware design, MCU8&9 is pulled up for MCU_BOOTMODE setting.

And now PBIST and LBIST are needed.

Could we change the POST sequence while eFuse programming in our factory without modifying the HW BOM?

SOC PN: TDA4VE88T5AALZRQ1

Thanks,