Other Parts Discussed in Thread: AM62P

Tool/software:

Hello

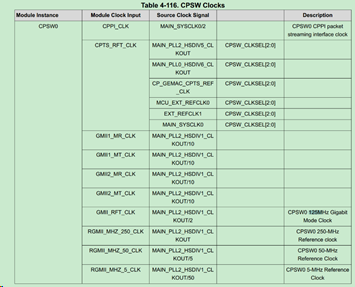

We try to modify the clock from 25MHz of 100 BASE to 1000 BASE of mac.

We changed the MAC control register bit 7 to gigabit mode, the current mac controll register is 0xa1, but the out put clock is still 25MHz, is there any thing we should check ?

Is there any clock divider we should check?

B.R.

Changxing DU