Other Parts Discussed in Thread: AM2432

Tool/software:

Hello team,

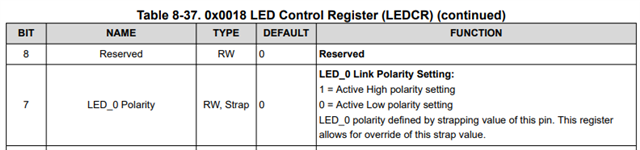

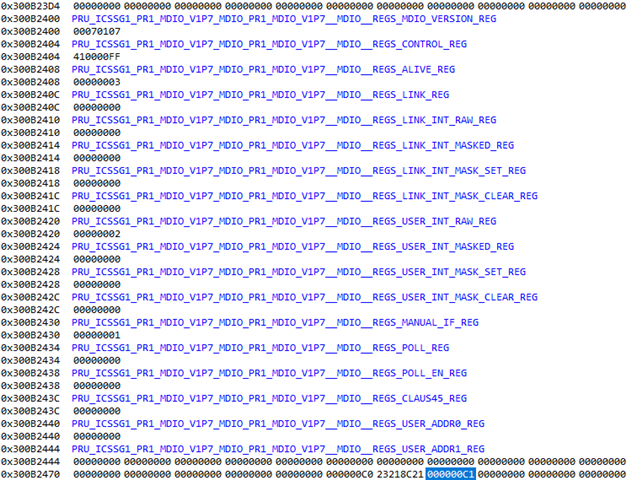

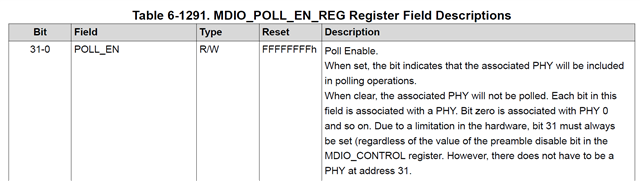

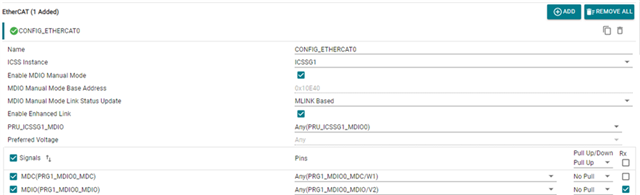

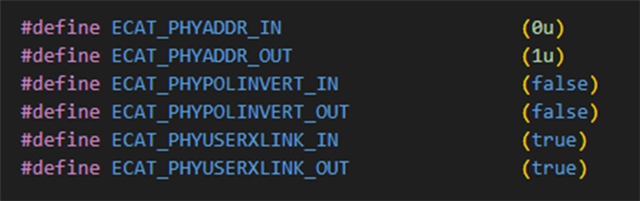

I develop EtherCAT subdevice application with AM2432 and de83822.

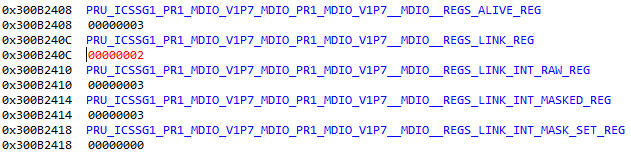

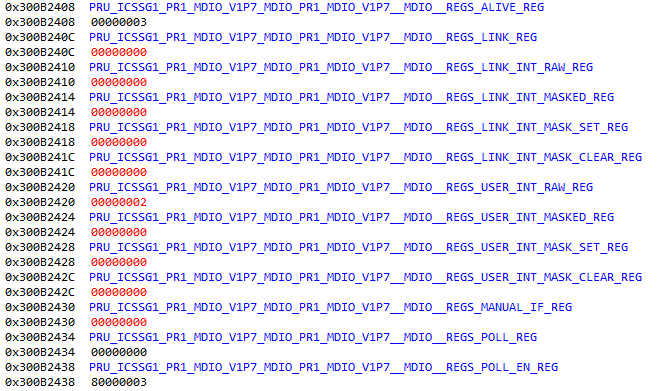

Link detection works fine via MDIO, but not via the PHY's GPIO.

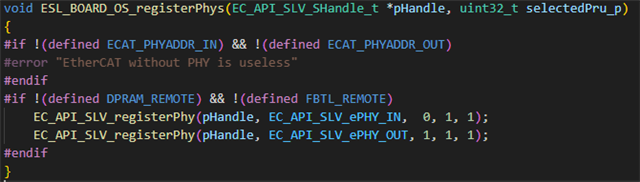

This is how I set it up.

However, not only will the link not be detected, but the link will not even be found.

Is there any other configuration required?

Best regard,

Oyama