Tool/software:

Hy,

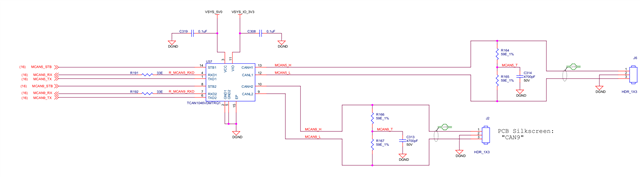

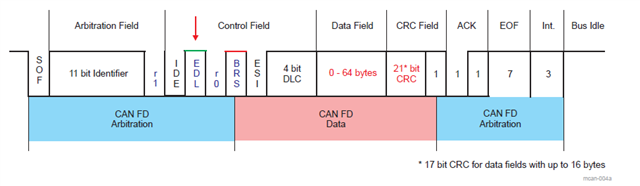

I am using the SDK: rtos-09_02_00_05 on a custom board that has the same schematic like the SK-TDA4VM (MCU_MCAN0, MCAN0, MCAN5 and MCAN9). As example I am following the pdk_jacinto_09_02_00_30/packages/ti/csl/example/mcan/mcanEvmLoopback/mcan_evm_loopback_app_main_k3.c source code.

I want to route the MCAN5 and MCAN9 IR to the MCU1_0 R5F processor. For configuring main MCAN IRQ I am using the following code:

static int32_t MCAN_CfgIrqRouterMain2Mcu(uint32_t devId, uint32_t offset, uint32_t intNum)

{

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

rmIrqReq.valid_params = TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.src_id = devId;

rmIrqReq.global_event = 0U;

rmIrqReq.src_index = 1U; /* mcanss_mcan_lvl_int Line 0 */

rmIrqReq.dst_id = TISCI_DEV_MCU_R5FSS0_CORE0;

rmIrqReq.dst_host_irq = intNum;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSet(&rmIrqReq, &rmIrqResp, SCICLIENT_SERVICE_WAIT_FOREVER);

if(CSL_PASS != retVal)

{

uart_write(DEBUG_UART, "Error in SciClient Interrupt Params Configuration!!!");

snprintf(buffer, sizeof(buffer), "offset: %d \n", offset);

uart_write(DEBUG_UART, buffer);

}

else

{

snprintf(buffer, sizeof(buffer),

"SciClient Interrupt Params Configuration passed for intNum: %08X \n", intNum);

uart_write(DEBUG_UART, buffer);

}

return retVal;

}

And for registering the interrupt:

static int32_t MCAN_regiterISR(uint32_t intNum, void f(uintptr_t))

{

int32_t configStatus = STW_SOK;

OsalRegisterIntrParams_t intrPrms;

OsalInterruptRetCode_e osalRetVal;

HwiP_Handle hwiHandle = NULL;

/* Enable CPU Interrupts and register ISR */

Osal_RegisterInterrupt_initParams(&intrPrms);

/* Populate the interrupt parameters */

intrPrms.corepacConfig.arg = (uintptr_t) NULL;

intrPrms.corepacConfig.isrRoutine = f;

intrPrms.corepacConfig.priority = 1U;

intrPrms.corepacConfig.corepacEventNum = 0U;

intrPrms.corepacConfig.intVecNum = intNum;

/* Register interrupts */

osalRetVal = Osal_RegisterInterrupt(&intrPrms, &hwiHandle);

if(OSAL_INT_SUCCESS != osalRetVal)

{

configStatus = CSL_EFAIL;

uart_write(DEBUG_UART, "Error in registering ISR!!!");

}

return configStatus;

}

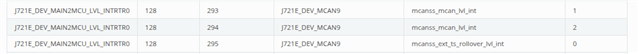

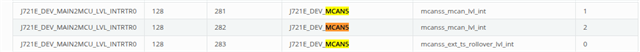

My aim is to test the external loopback mode between MCAN5 and MCAN9. As rmIrqReq.src_id I am configuring TISCI_DEV_MCAN5 and TISCI_DEV_MCAN9, and src_index =1 but I don't know for rmIrqReq.dst_host_irq what should I configure? The dst_id is TISCI_DEV_MCU_R5FSS0_CORE0 for both.

Regards,

Tamas