Tool/software:

All,

My assigned focus customer has a question about the MMC0 speeds:

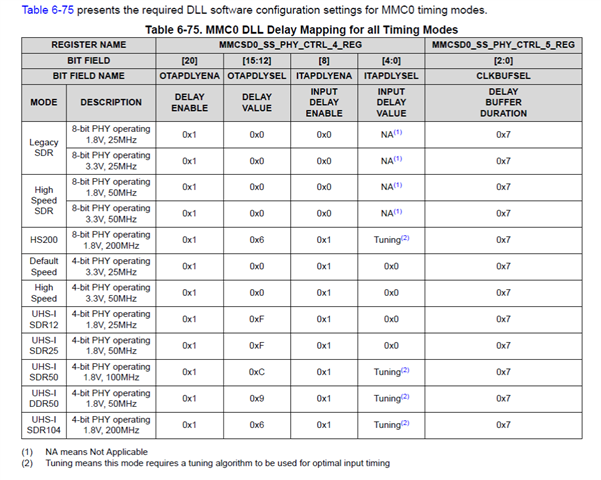

Is DDR Mode (4-bit, 8-bit) at up to 50 MHz supported? Based on the table below, it seems the fastest we can do at 3.3V is 52MHz at 8 bits.

Please advise.

I have asked for clarity as to his goals. I am assuming it is the fastest speeds possible. Would that be the HS200 8bit at 200 MHz rather than the 3.3v @ 50MHz he notes above?

Best Regards,

Blake