Tool/software:

Issue Description

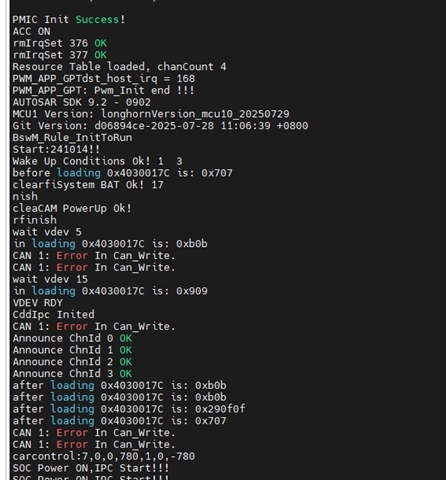

During SPI debugging, we observed inconsistent data between the actual MISO signal and the received data printed by the system. The problem was reproduced in TI SDK's reference example:mcusw/mcal_drv/mcal/examples/Spi.

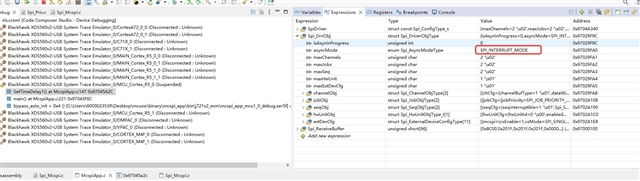

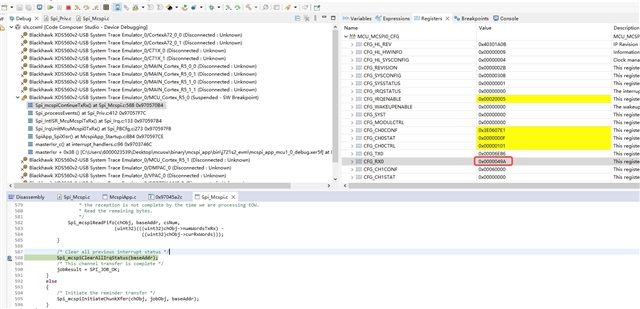

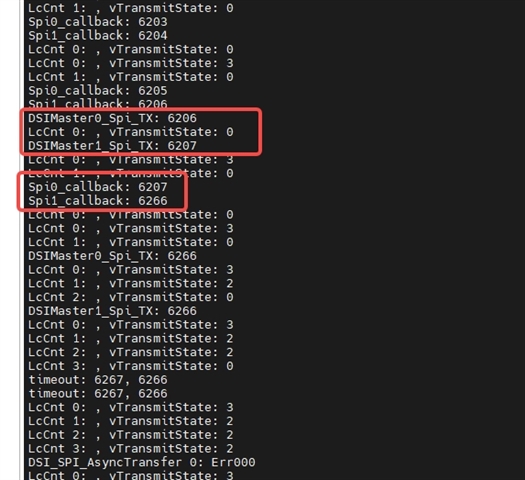

Observed Behavior

- Physical MISO Signal (captured via logic analyzer)

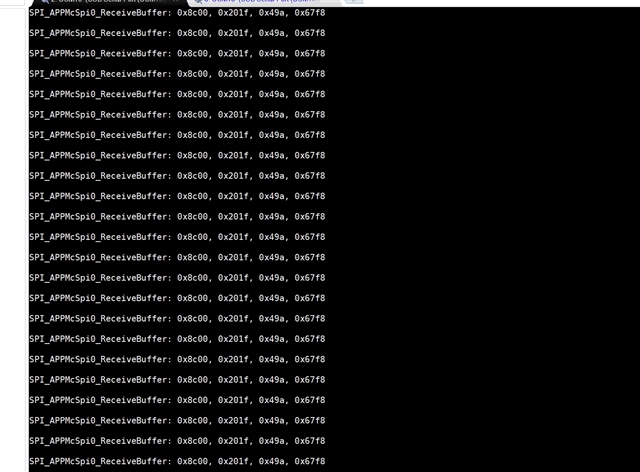

2. Printed Data (from system log):

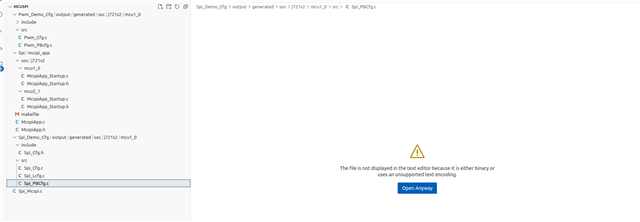

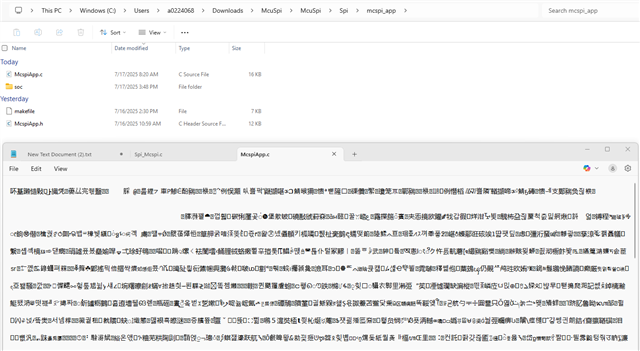

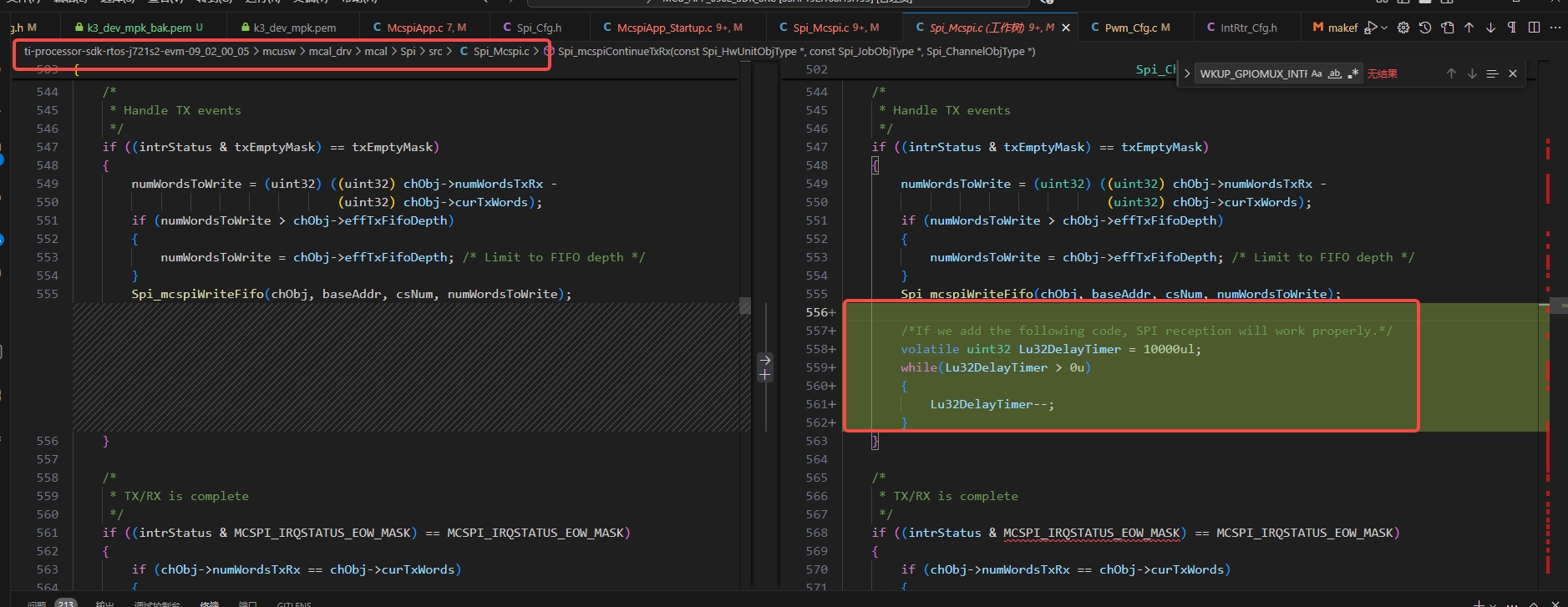

The SPI reception data is now printed correctly after applying the modifications depicted in the following figure to Spi_Mcspi.c.

Attached is my code implementation. Could TI experts review whether there are issues in the SPI software configuration?