Tool/software:

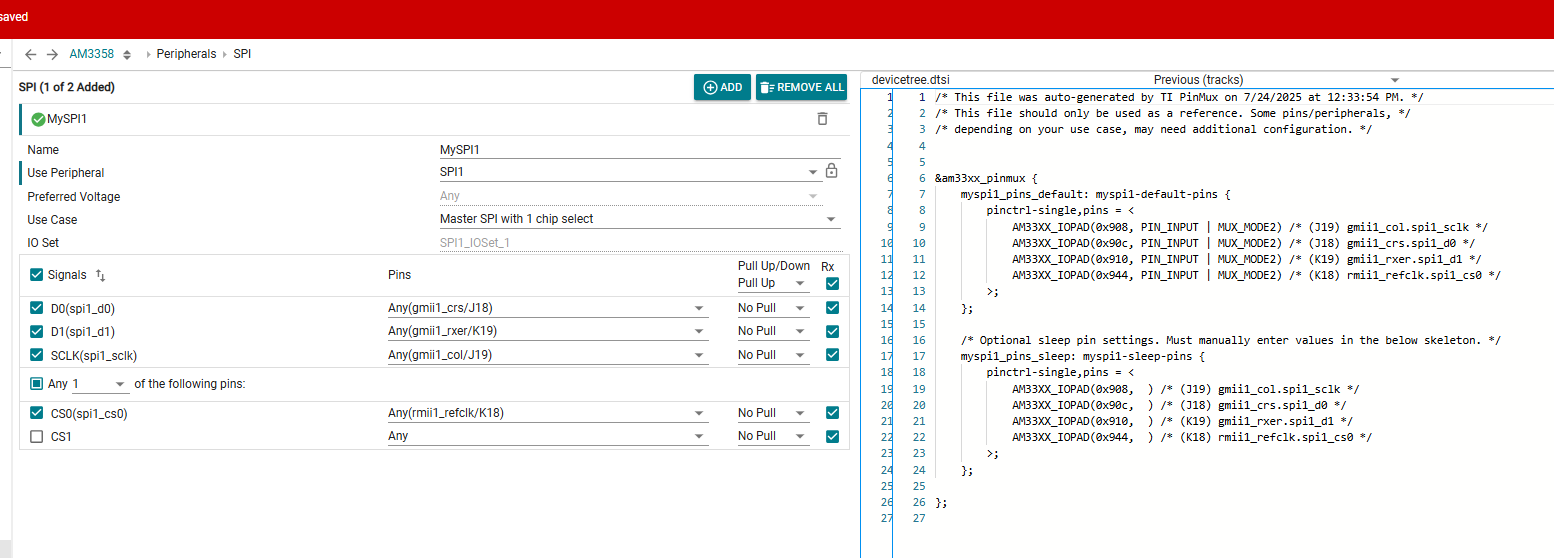

Has anyone seen SPI1 CS0 stay high on an OSD3358 when the bus is routed over the MCASP0 pins (MODE 3)? My SCLK only appeared after I set its pad to PIN_INPUT_PULLUP | RXACTIVE—a quirk that fixed the clock—but CS0 never goes low during transfers to a SPI slave module, so all reads return 0xFF. I’m using the usual DT pins (SCLK/MISO as input‑pullup, MOSI/CS0 as output‑pullup) and haven’t yet tried unusual methods like making CS0 an input. Before I start flipping properties at random, is there a known pad‑mux or device‑tree tweak to get the McSPI master to assert CS low in this setup, or a minimal example that proves it works?