Part Number: AM2732

Other Parts Discussed in Thread: TMDS273EVM,

Tool/software:

Hi All,

I tried connecting and writing using XDS200, but I couldn't connect properly.

Please tell me the settings necessary to connect and write correctly.

The EVM's AM273x is Revision A, but I think it is currently Revision C.

Is it necessary to support secure areas?

1. Import the initial connection verification environment (hello_world_am273x-evm_r5fss0-0_nortos_ti-arm-clang)

2. Click evmAM273x.ccxml, change Connection to XDS2xx USB Debug Probe from the Basic tab.

Change Board on Device from evmAM273x to AM273x.

When you perform Test Connection, the following OK message is displayed.

The JTAG IR Integrity scan-test has succeeded.

The JTAG DR Integrity scan-test has succeeded.

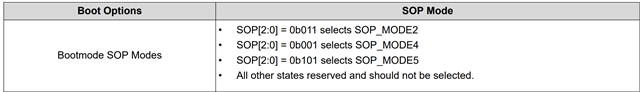

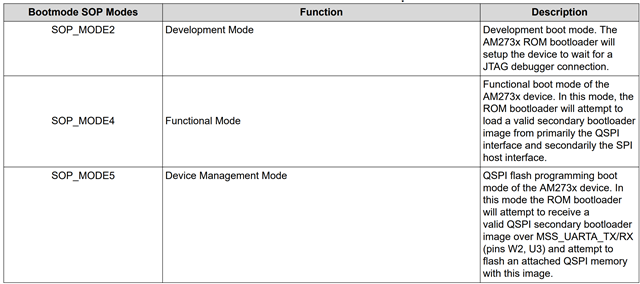

3. Set the SOP to NOBOOT MODE and perform Debug. The following error will be displayed.

Cortex_R5_0: AM273x Cortex_R5_0: Trouble Writing Memory Block at 0x0 on Page 0 of Length 0x40: (Error -1065 @ 0x0) Unable to access device memory. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 12.7.0.00130) Cortex_R5_0: File Loader: Verification failed: Target failed to write 0x00000000 Cortex_R5_0: GEL: File: C:\work\Rader\mid_radar_mainboard_test\ipc_notify_echo_am273x-evm_r5fss0-0_freertos_ti-arm-clang\Debug\ipc_notify_echo_am273x-evm_r5fss0-0_freertos_ti-arm-clang.out: Load failed.

4. Even when SOP is set to QSPI Boot, “C” is not sent to the serial port used by XDS200. Python for QPSI writing cannot be used.

5. When the SOP is set to MODE6 (SOP0=0, SOP1=1, SOP2=1) and debugging is performed, execution is not possible, but the error message changes as follows.

*This mode is only available for Secure-compatible chips.

Cortex_R5_0: AM273x Cortex_R5_0: Trouble Setting Breakpoint with the Action "Process CIO" at 0x10281588: (Error -1066 @ 0x10281588) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 12.7.0.00130) Cortex_R5_0: Breakpoint Manager: Retrying with a AET breakpoint Cortex_R5_0: Trouble Setting Breakpoint with the Action "Finish Auto Run" at 0x10280100: (Error -1066 @ 0x10280100) Unable to set/clear requested breakpoint. Verify that the breakpoint address is in valid memory. (Emulation package 12.7.0.00130) Cortex_R5_0: Breakpoint Manager: Retrying with a AET breakpoint Cortex_R5_1: Error connecting to the target: (Error -1170 @ 0x0) Unable to access the DAP. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 12.7.0.00130)

Could you please advise on a solution based on this information?

Best Regards,

Ito