Other Parts Discussed in Thread: AM69

Tool/software:

Hi,

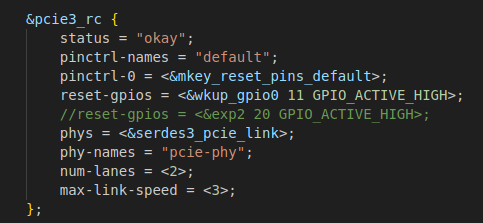

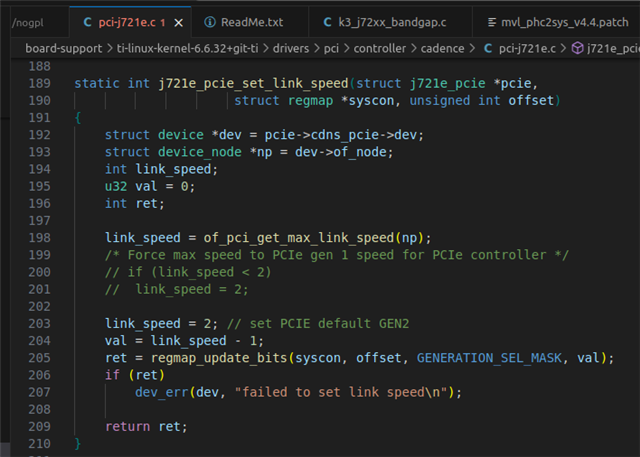

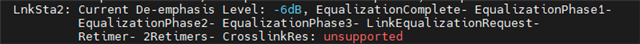

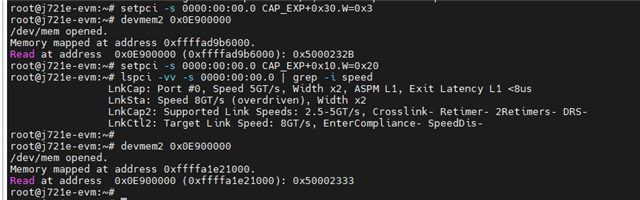

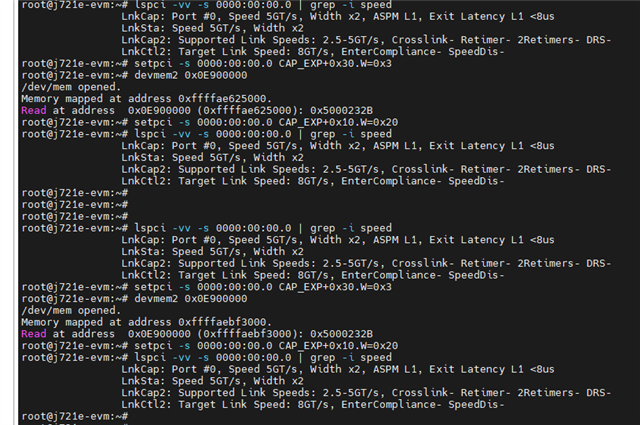

Because if configured as GEN3 during startup, there is a probability that the external Switch chip cannot be recognized, resulting in driver loading failure. Therefore, GEN2 is defaulted during startup. Is there a way to modify the PCIE rate from GEN2 to GEN3 after TDA4 startup?

Regards,

Yang