Tool/software:

Hi,

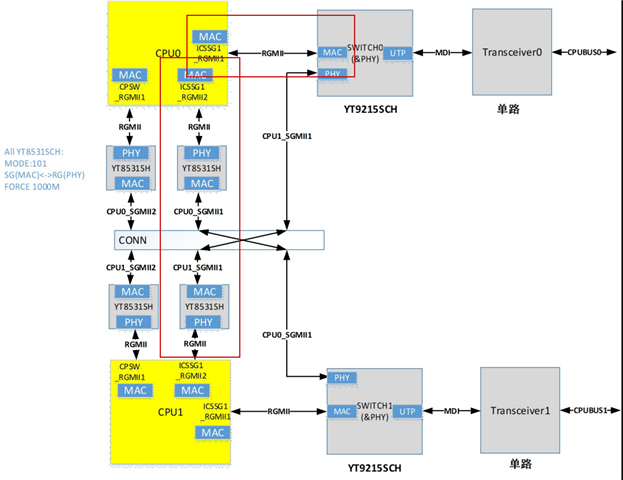

Two modules are communication, for example at both ends of CPUBUS0 A module and B module, they will send and receive data to each other.

During running, after unplugging the A module with am6442 and using Cortex-A53 core, it happened that ICSSG1_RGMII1 and ICSSG1_RGMII2 are unable to receive any data, receiving interrupt is not triggered.

And at this time sending is OK.

Then PRU_STAT memory data are as follows:

offset=0xF8 0xFC 0x138 0x13C these values are not incremented when send and receive data with module B.

offset=0x10/0x18/0x248/0x24c/0x250/0x254 these values are always incremented send and receive data with module B.

But this time the receive interrupt are not triggered for ICSSG1_RGMII1 and ICSSG1_RGMII2 ports and send interrupt is triggered OK.

We read PRU_MII_G_RT_MII_G_RT registers.

stats->rx_crc_error_frames + stats->rx_mii_error_frames + stats->rx_odd_nibble_frames + stats->rx_max_size_error_frames + stats->rx_min_size_error_frames + stats->rx_overrun_frames; →They are zero in total.

stats->tx_odd_nibble_frames + stats->tx_max_size_error_frames + stats->tx_min_size_error_frames + stats->tx_underflow_errors; →They are zero in total.

rx_good_frames register and rx_total_bytes register values are incremented.

tx_good_frames register and tx_total_bytes register values are incremented.

Why are two ICSSG1_RGMII1 and ICSSG1_RGMII2 ports unable to receive data?

Please help and support some advice, Thank you.