Tool/software:

Hello,

for AM62P54 LPDDR4 3200Mbps, the std PCB material is OK or need higher frequency material? and what's the restriction?

thanks!

Hello

some questions as below, pls help to reply, thanks!

Impedance control for LPDDR4: as TI guideline, LPDDR4 point to point signals should be routed as single end 40R, all signals should be routed in inner layer, and also keep signal space as 3w rule

Questions:

1. yes these can be increased

2. Yes, but i would recommend board simulation to ensure no intersymbol interference or crosstalk

3. Signal can be routed on outer layer, but again, i would recommend board simulations. Ensure proper ground references for those layers, proper impedance matching, and keep propagation delay matching as specified in the app note.

If you only have one LPDDR4 device, you won't need to do any T-branching of DQ signals. Multiple LPDDR4 devices is not supported.

Regards,

James

Hello,

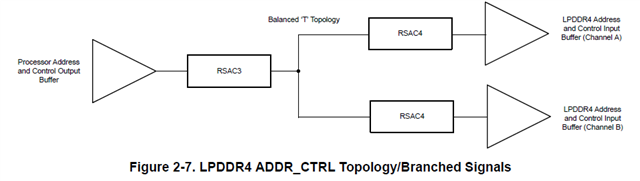

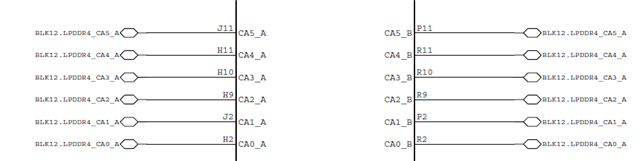

thanks for reply, i have additional question regarding T-branching, as below show, for CA lines, does need T-branching? or fly-by topology is applicable? or any recommendation?

thanks!

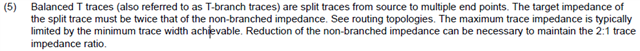

below is the screenshot from "AM62Ax, AM62Px, AM62Dx LPDDR4 Board Design and Layout Guidelines", do CA lines need to follow below rules? Here i want confirm with you.