Tool/software:

I use a DRA829J-Q1 supplied with two PMIC according PDN-0C on my HW.

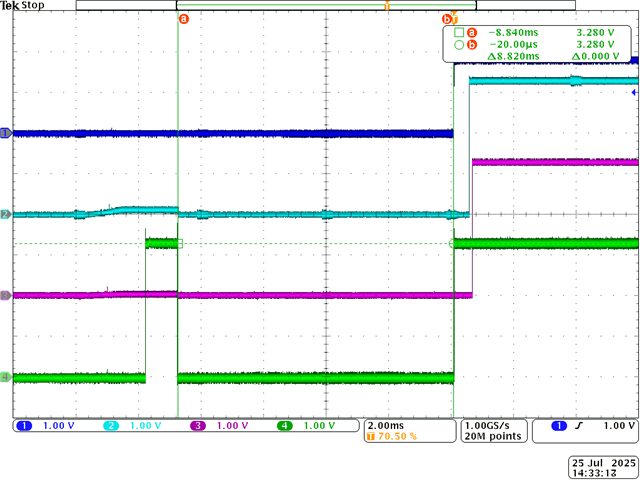

At Startup, PORz_out (green) is driven high before MCU_PORz (deep blue) is released by PMIC.

light blue: MCU_RESETSTATz

purple: RESETSTATz

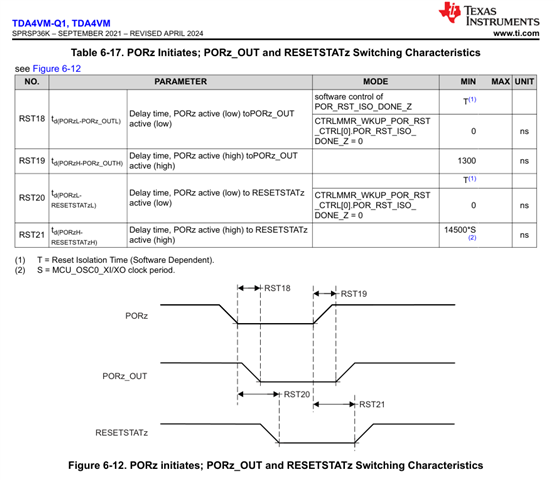

My expectation would be PORz_out going high 1500ns after MCU_PORz as stated in SPRSP35K table 6-8.

What can be the reason for the previous pulse? Is this a critical behaviour, as only usage of PORz_out in my HW is disabling Bootmode buffers similar to EVM?

Regards, Peter