Other Parts Discussed in Thread: AM69

Tool/software:

This is a continuation of an older thread, which was locked due to inactivity:

SK-AM69: Help with enabling SERDES/ACSPCIe output on SK-AM69

Hi Takuma Fujiwara , I'm sorry that I did not keep up with the older thread. In your last comment (here), you mentioned that you were in the process of trying to see if you could remove some circuitry from your SK-AM69 board to see if that is somehow having an effect. I'm guessing at this point that you either didn't have the time to try that yet, or it didn't make a difference for you -- but if you have any updates, please let me know.

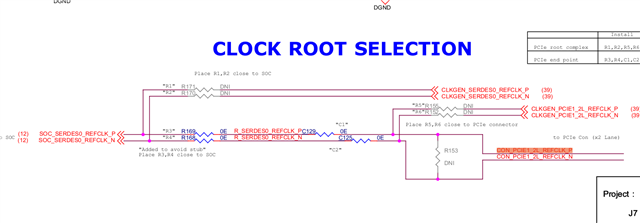

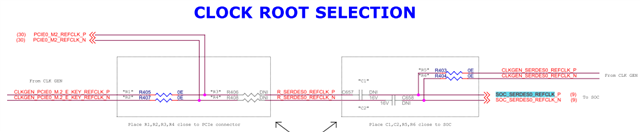

You recommended that we could copy what the SK-AM69 is doing with the external clock generation circuitry, but that is precisely what I am trying to avoid, due to the BOM cost that you mentioned, as well as the PCB space it would consume (every little bit counts). So I'm still looking for a way to give myself confidence that our AM69 PCB design will work without that additional circuitry.

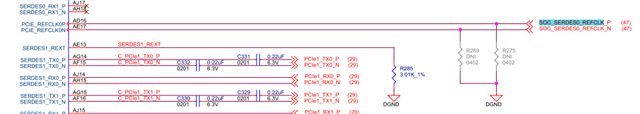

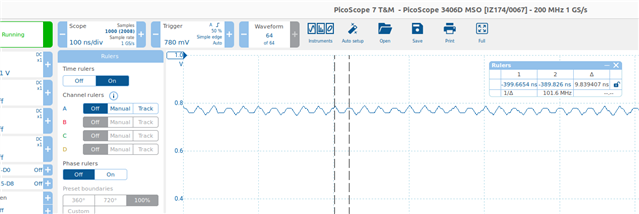

I was looking back over what we have done so far. Based on the oscilloscope screenshot that you posted in your last comment, it seems that you were able to add the 50Ω termination resistors to your board, because we are both seeing ~1.8V on TP106 after executing devmem2 0x118090 w 0x01000002 in order to de-assert the power down bit for PCIe1.

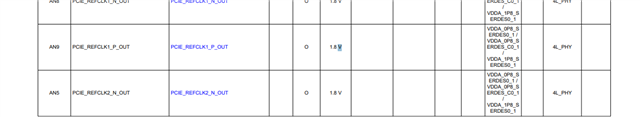

I am thinking that perhaps this 1.8V could be a clue as to what is possibly being misconfigured inside the AM69. The SERDES REFCLK_OUT pins, such as AN9 which is connected to TP106, should be HCSL (High-Speed Current-Steering Logic), so that the output pin switches between driving 0mA (when "low") and ~14mA (when "high"). When that current is passed through the 50Ω resistor to ground, the resulting voltage at the test point should be either 0V (when "low") or ~0.7V (when "high"). At no point should an HCSL output pin exhibit a voltage of 1.8V, as far as I understand it. With TI's internal knowledge of the silicon, does it make any sense that 1.8V should be measured on these pins? Is there some misconfiguration of the SERDES that could make this happen?

Thanks for your continued help with this!

Best regards,

Dave