Other Parts Discussed in Thread: TDA4VH

Tool/software:

The TDA4VH TRM suggests that there is a 16KB L1D partition available as SRAM and separate from L1D cache that can be used for LUT and histogram. Is this correct and can this SRAM be used local for storage of scalar operands.? Assuming YES, we would like to know how to configure the MMU to enable this C7x L1D SRAM if it exists. We are writing C7x code using DSPLIB environment as a starting point.

- We are using J784S4 RTOS SDK 10.01.00.04 on Ubuntu 22.04.1 host

- We have followed the DSPLIB build instructions at this link: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/10_01_00_04/exports/docs/dsplib/docs/user_guide/build_instructions_linux.html

- We have followed the CCS baremetal instructions at this link: https://software-dl.ti.com/jacinto7/esd/processor-sdk-rtos-j784s4/latest/exports/docs/psdk_rtos/docs/user_guide/ccs_setup_j784s4.html#debugging-without-hlos-running-on-a72-rtos-only-baremetal

- We are using a J784S4XG01EVM rev PROC141E5(001) for our testing

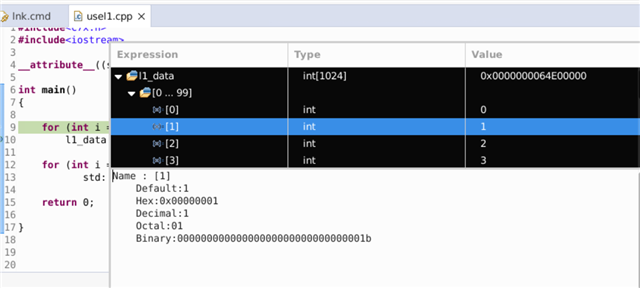

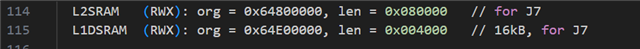

From the DSPLIB linker command file we guessed that the L1D SRAM is mapped at address 0x64800000, but when we link variables there, our application does not execute correctly and we are not able to modify those address ranges with CCS.

.

.