Tool/software:

Hi,

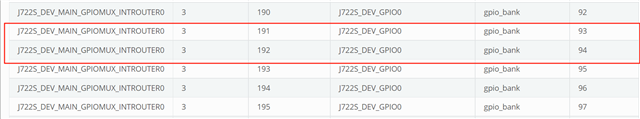

mcu20 requires the use of 191 and 192 banks Interrupt

However, due to the occupation of linux, after attempting to modify it now,

the linux gpio cannot be used, please fix my modification.

main_gpio_intr: interrupt-controller@a00000 {

compatible = "ti,sci-intr";

reg = <0x00 0x00a00000 0x00 0x800>;

ti,intr-trigger-type = <1>;

interrupt-controller;

interrupt-parent = <&gic500>;

#interrupt-cells = <1>;

ti,sci = <&dmsc>;

ti,sci-dev-id = <3>;

ti,interrupt-ranges = <0 32 1>, <3 35 3>; // 190,193-195

};

main_gpio1_intr: interrupt-controller@a00000 {

compatible = "ti,sci-intr";

reg = <0x00 0x00a00000 0x00 0x800>;

ti,intr-trigger-type = <1>;

interrupt-controller;

interrupt-parent = <&gic500>;

#interrupt-cells = <1>;

ti,sci = <&dmsc>;

ti,sci-dev-id = <3>;

ti,interrupt-ranges = <0 38 6>;

};

main_gpio0: gpio@600000 {

compatible = "ti,am64-gpio", "ti,keystone-gpio";

reg = <0x00 0x00600000 0x00 0x100>;

gpio-controller;

#gpio-cells = <2>;

interrupt-parent = <&main_gpio_intr>;

interrupts = <190>, /* <191>, <192>, */

<193>, <194>, <195>;

interrupt-controller;

#interrupt-cells = <2>;

ti,davinci-gpio-unbanked = <0>;

power-domains = <&k3_pds 77 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 77 0>;

clock-names = "gpio";

};

main_gpio1: gpio@601000 {

compatible = "ti,am64-gpio", "ti,keystone-gpio";

reg = <0x00 0x00601000 0x00 0x100>;

gpio-controller;

#gpio-cells = <2>;

interrupt-parent = <&main_gpio1_intr>;

interrupts = <180>, <181>, <182>,

<183>, <184>, <185>;

interrupt-controller;

#interrupt-cells = <2>;

ti,davinci-gpio-unbanked = <0>;

power-domains = <&k3_pds 78 TI_SCI_PD_EXCLUSIVE>;

clocks = <&k3_clks 78 0>;

clock-names = "gpio";

};

log:

1.624724] am65-cpsw-nuss 8000000.ethernet: initializing am65 cpsw nuss version 0x6BA01903, cpsw version 0x6BA81903 Ports: 3 quirks:00000006 [ 1.637795] am65-cpsw-nuss 8000000.ethernet: initialized cpsw ale version 1.5 [ 1.644929] am65-cpsw-nuss 8000000.ethernet: ALE Table size 512, Policers 32 [ 1.652674] am65-cpsw-nuss 8000000.ethernet: CPTS ver 0x4e8a010d, freq:500000000, add_val:1 pps:0 [ 1.670756] am65-cpsw-nuss 8000000.ethernet: set new flow-id-base 19 [ 1.685140] mmc0: CQHCI version 5.10 [ 1.686231] davinci_gpio 600000.gpio: error -ENXIO: IRQ index 4 not found [ 1.700980] clk: Disabling unused clocks [ 1.710242] PM: genpd: Disabling unused power domains [ 1.715397] ALSA device list: [ 1.718435] No soundcards found. [ 1.735577] mmc0: SDHCI controller on fa10000.mmc [fa10000.mmc] using ADMA 64-bit [ 1.743279] Waiting for root device PARTUUID=d73bf4db-02... [ 1.865975] mmc0: Command Queue Engine enabled [ 1.870454] mmc0: new HS200 MMC card at address 0001 [ 1.876838] mmcblk0: mmc0:0001 A8A398 7.28 GiB [ 1.883008] mmcblk0: p1 p2 p3 p4 < p5 p6 > [ 1.888283] mmcblk0boot0: mmc0:0001 A8A398 4.00 MiB [ 1.894148] mmcblk0boot1: mmc0:0001 A8A398 4.00 MiB [ 1.899917] mmcblk0rpmb: mmc0:0001 A8A398 4.00 MiB, chardev (239:0) [ 11.785463] i2c 0-0048: deferred probe pending: i2c: supplier 600000.gpio not ready [ 11.793148] platform fa00000.mmc: deferred probe pending: platform: supplier regulator-TLV71033 not ready [ 11.802702] platform regulator-TLV71033: deferred probe pending: platform: supplier 600000.gpio not ready [ 11.812253] platform 2b300050.target-module: deferred probe pending: (reason unknown)

Regards,

Cesar