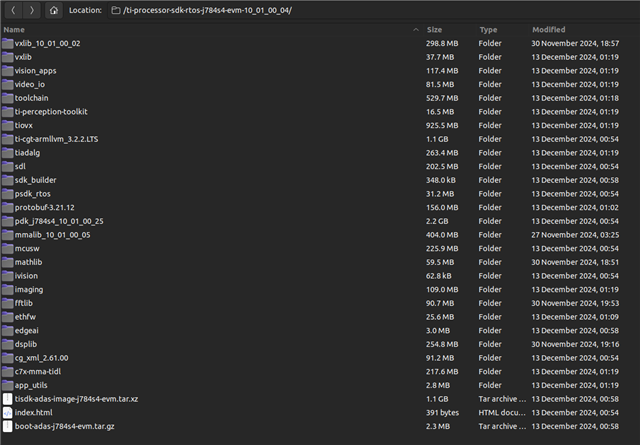

Part Number: PROCESSOR-SDK-J784S4

Tool/software:

Hi, I'm using J784S4's TI SDL library to run pbist. Planning to do it during shutdown

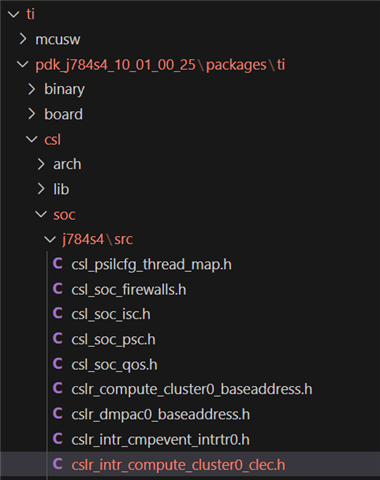

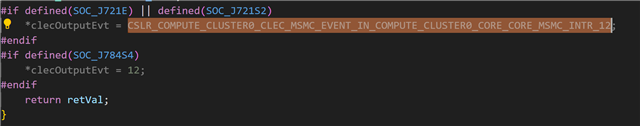

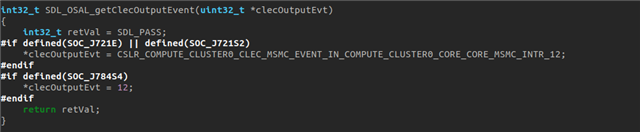

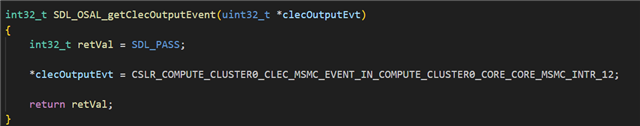

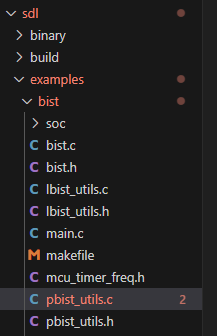

I'm not able to fine a lot of definitions for macros used in example library.

which are used in pbist_utils.c

for example :