Tool/software:

Hi

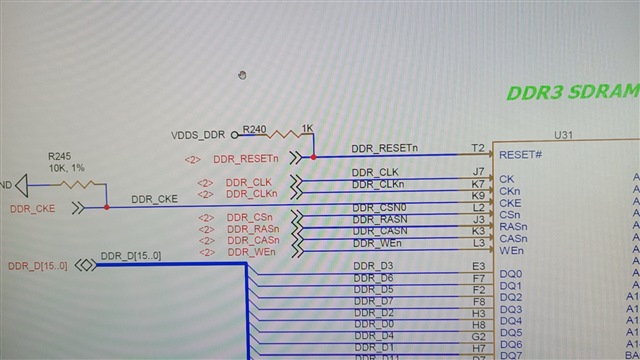

Customer are checking if there are any requirement of this DDR_RESETn resistor.

Do this resistor have to be a pull-up or pull-down resistor? What is the value of this resistor, any recommendation?

Thanks

Zekun

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi

Customer are checking if there are any requirement of this DDR_RESETn resistor.

Do this resistor have to be a pull-up or pull-down resistor? What is the value of this resistor, any recommendation?

Thanks

Zekun

The pull-up resistor on DDR_RESET is only needed if you are using low power DeepSleep mode which requires the DDR_RESETn signal to be high when most of the processor is in the OFF state. If you are not using DeepSleep mode, you do not need the pull up.

The value of the pull up should be what is on the EVM, 1K

Regards,

James

No pull up is needed if the down use low-power mode, they should just not populate it. If pull up is there, there is a slight risk high current draw during power up, since the DDR may drive signals inadvertently when out of reset.

Regards,

James

Hi James

I have one confusion.

>> If pull up is there, there is a slight risk high current draw during power up, since the DDR may drive signals inadvertently when out of reset.

If there is a risk using pull-up, why do we use this in low-power-mode? Don't this design bring EVM a risk?

Thanks

Zekun

Hi Zekun, yes you are correct, there is a slight risk in EVM design, but this is the only way to support low power modes on EVM. The AM335x DDR controller and PHY do not properly drive the RESET signal high during low power modes.

As mentioned before, we have never seen a functional issue with the pull up.

Regards,

James

Hi James

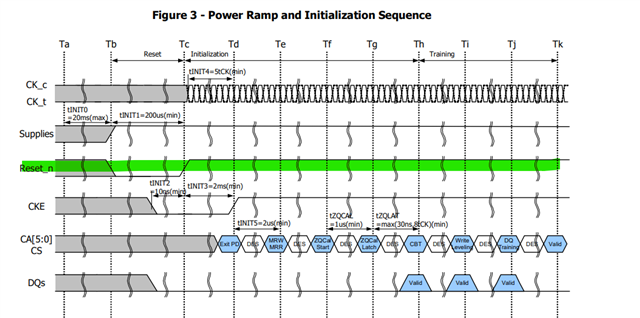

Now customer meet one urgent issue on a mass production project, and want to check what is the logic behind the reset signal RESETN output from the AM3352 to the DDR? What are the preconditions after power-on?

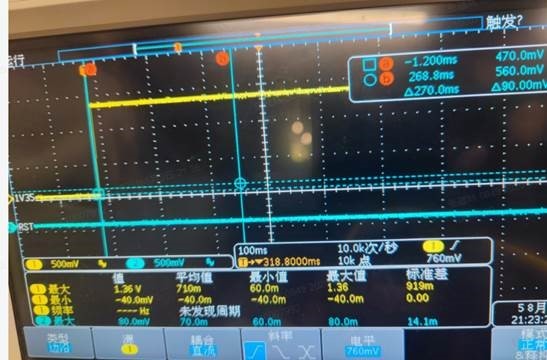

Note: The DDR section uses a 1.35V power supply. Two prototypes currently have this signal stuck low and not pulled high. Replacing the CPU and DDR with new ones hasn't resolved the issue. I've also confirmed that the connection between the two pads for this signal is working properly. What is the possible reason?

Abnormal:

Normal:

Regards

Zekun

Zekun, the RESET_n signal will go high during DDR initialization procedure, which is executed in the bootloader. Is the abnormal scope shot taken when the device is going through the normal boot procedure? It looks like there may be a boot issue with the abnormal scope shot before the DDR initialization code is ever executed. I would check the boot media and ensure the ROM is retrieving the bootloader correctly. Is this only happening on some boards?

Regards,

James

Note: The DDR section uses a 1.35V power supply. Two prototypes currently have this signal stuck low and not pulled high. Replacing the CPU and DDR with new ones hasn't resolved the issue. I've also confirmed that the connection between the two pads for this signal is working properly. What is the possible reason?Abnormal:

Hi Zekun

DDR reset signal is high and will be pull down for a short time then be pull up again, thus reset the DDR

if the DDR_RSTn is always pulled down, maybe this is caused by some components failure in the HW board, such as capacitor in the circuit.

if only one or two HW boards has problem, please let customer check the components in the board

Regards

Semon