Other Parts Discussed in Thread: SK-AM62A-LP, SYSCONFIG

Tool/software:

Hi, TI expert

I would like to inquire about the SBL startup related issues of AM62A. The current development environment is as follows.

SDK version: V10.01.00

Board: sk-am62a-lp

Startup method: SBL

Storage: only eMMC

Our design aims to perform OTA, including all firmware for MCU R5F/DM R5F/A53's A/B booting. At first, SPL startup was considered, but considering the requirements of vehicle network management and wake-up time, SBL startup was changed. This way, MCU R5F can start faster and communicate with other ECUs in the vehicle more quickly. Based on the requirements of SBL startup and OTA upgrade, we have studied the relevant code for SBL startup and found that in order to achieve our needs, the selection logic for A/B startup must be included in the sbl_emmc_linux_stage1 code,right?

However, we have some doubts and would like to ask TI experts:

Q1. Is it feasible to place the selection logic for A/B startup in the code of sbl_emmcnlinux_multistage1?If feasible, please continue to help take a look at the following issues.But if it is not OK, please help provide advice or guidance.

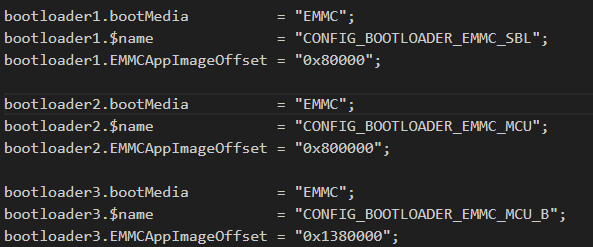

Q2. The firmware of MCU R5F defaults to flashing at location 0x800000 and is written by examples/drivers/boot/sbl_emmc_linux_multistage/sbl_emmc_linux_stage1/am62ax-sk/r5fss0-0_nortos/example.syscfg . It was configured before compilation. Can sbl_emmc_linux_stage1 dynamically select the address to load MCU R5F firmware? For example, partition A chooses to load location 0x800000, while partition B chooses to load another location such as x1800000.

Q3. Can sbl_emmc_linux_stage2 also support dynamic selection to load other firmware addresses such as HSM/DM?

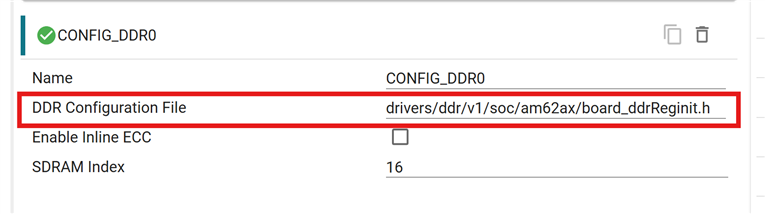

Q4. Is the initialization of DDR carried out in sbl_emmc_linux_stage1? How to configure DDR configuration generated by Sysconfig in code?

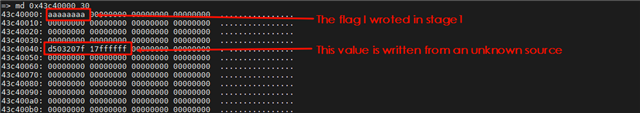

Q5. In what way can sbl_emmc_linux_stage1 transmit information to sbl_emmc_linux_stage2 or subsequent Linux applications? For example, certain registers or DDR reserved address segments .The purpose of doing so is to use OTA strategy, so that subsequent firmware, such as sbl_emmc_linux_stage2/uboot/Linux APP, can directly perceive the A/B partition selected by sbl_emmc_linux_stage1.

Q6. Due to our configuration of MCU R5F and Linux heartbeat, MCU R5F can sense the survival status of Linux. May I ask how to achieve only A53 reset if the Linux kernel freezes during the startup phase?