Tool/software:

Hi

Recently, a device using a 66AK2H06 processor reported a single-bit error in the SL2/MSMC memory that persisted. We have conducted simulation tests and would appreciate your feedback and follow-up as soon as possible.

Symptom: A single-bit error occurred in the constant data of the 66AK2H06 processor's SL2 memory. The memory address was 0x0C3A4048, and the memory data changed from 0x0C38CB04 to 0x0C18CB04 (Bit 21 changed from 1 to 0). The device was powered on and running for nine months, and the log showed two single-bit error corrections in the SL2 memory.

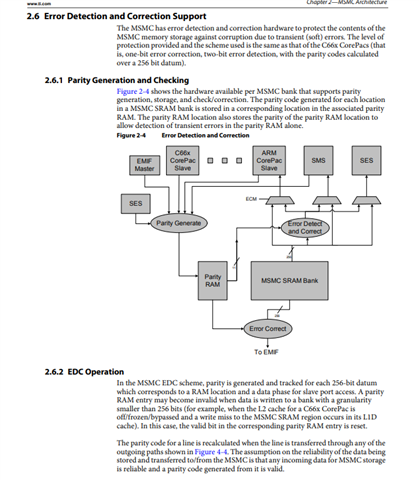

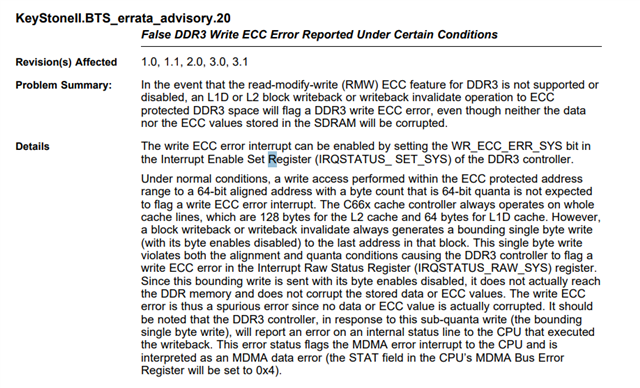

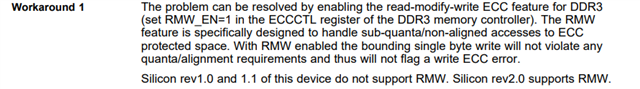

Problem Analysis: The suspected cause of the problem is a write operation to other data in the same SL2 memory subbank. The small-scale write caused the ECC checksum to be temporarily invalid, which, combined with particle radiation, caused the single-bit error in the SL2 memory to persist.

Simulation test: Disable the SL2 memory background scanning function, compare large and small data writes to the same subbank, simulate a single-bit error in the same subbank, and observe whether accessing the erroneous data can trigger an ECC interrupt.

Regards

Zekun