Other Parts Discussed in Thread: AM62L,

Tool/software:

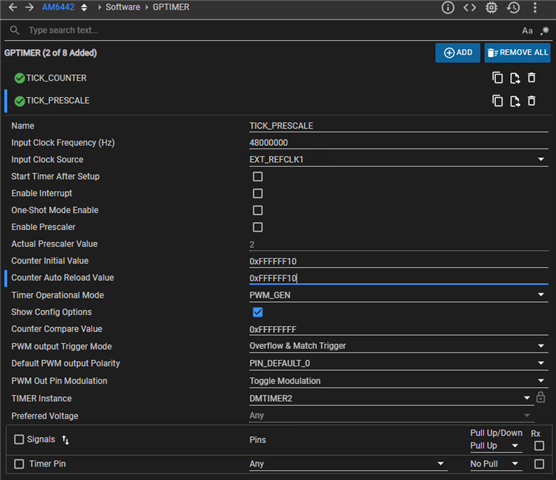

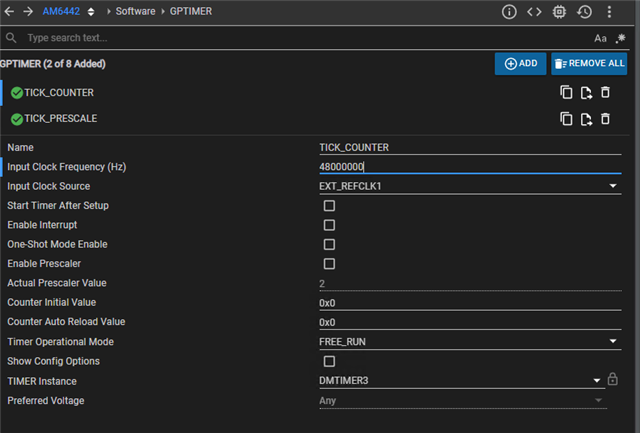

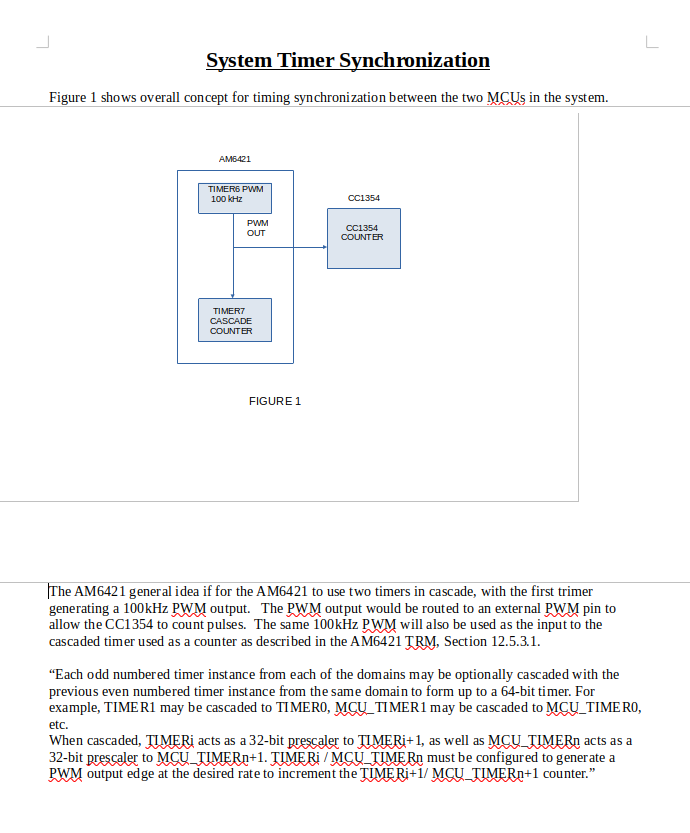

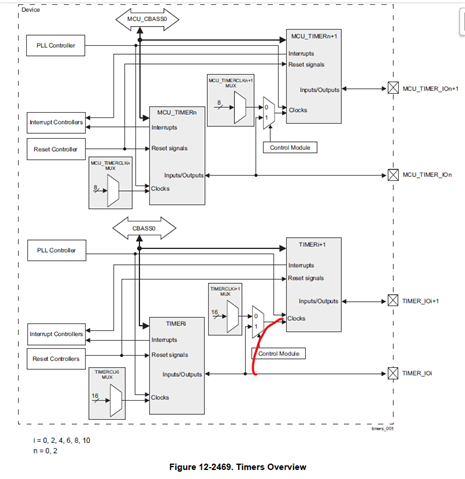

My design has multiple processors running from different clocks. To synchronize critical timing, I am trying to use EXT_REFCLK1 to run two cascaded timers. The prescale timer will provide a 10uS tick for the second free running timer. I have chosen TIMER2 as the 10uS tick generator and TIMER3 to count 10uS ticks. From the AM64x TRM, I found the CTRLMMR_TIMER3_CTRL CASCADE_EN bit in Section 5.1.1.5.65. My question is regarding how to program this register. I don't see any way to set this up from within the SysCfg system, and I can't find any example or an API that show how to handle this step during startup and system initialization