Tool/software:

Hello,

We are working on a PCIe link between a Jacinto J784s4 as Root Complex and a custom FPGA endpoint.

Our use case requires using multiple PCIe BARs on the FPGA. For certain flows, we would like to designate one BAR as an I/O BAR (rather than memory BAR) in order to have the ARM CPU perform direct I/O read/write transactions. The goal is to separate traffic, prevent posted transactions from blocking critical commands, and prioritize certain controls via the I/O BAR.

After reviewing the TRM (section 12.2.3.3.6), we noticed that "I/O Read/Write in outbound direction in RP mode" is listed among supported transactions.

Moreover, we tested it and saw the IO BAR assigned:

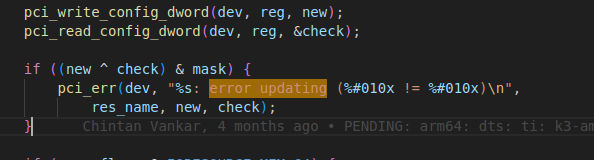

[ 0.613253] pci_bus 0000:00: root bus resource [bus 00-ff] [ 0.613259] pci_bus 0000:00: root bus resource [io 0x0000-0xffff] (bus address [0x10001000-0x10010fff]) [ 0.613263] pci_bus 0000:00: root bus resource [mem 0x10011000-0x17ffffff] [ 0.613293] pci 0000:00:00.0: [104c:b012] type 01 class 0x060400 [ 0.613298] pci_bus 0000:00: 2-byte config write to 0000:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 0.613406] pci 0000:00:00.0: supports D1 [ 0.613409] pci 0000:00:00.0: PME# supported from D0 D1 D3hot [ 0.615349] pci 0000:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 0.616014] pci 0000:01:00.0: [10ee:9034] type 00 class 0x058000 [ 0.620254] pci 0000:01:00.0: reg 0x10: initial BAR value 0x00000000 invalid [ 0.620258] pci 0000:01:00.0: reg 0x10: [io size 0x8000] [ 0.620281] pci 0000:01:00.0: reg 0x14: [mem 0x00000000-0x001fffff] [ 0.641938] pci_bus 0000:01: busn_res: [bus 01-ff] end is updated to 01 [ 0.641957] pci 0000:00:00.0: BAR 14: assigned [mem 0x10200000-0x103fffff] [ 0.641962] pci 0000:00:00.0: BAR 13: assigned [io 0x8000-0xffff] [ 0.641966] pci 0000:01:00.0: BAR 1: assigned [mem 0x10200000-0x103fffff] [ 0.646188] pci 0000:01:00.0: BAR 0: assigned [io 0x8000-0xffff] [ 0.646235] pci 0000:01:00.0: BAR 0: error updating (0x10009001 != 0x10008001) [ 0.653446] pci 0000:00:00.0: PCI bridge to [bus 01] [ 0.653451] pci 0000:00:00.0: bridge window [io 0x8000-0xffff] [ 0.653458] pci 0000:00:00.0: bridge window [mem 0x10200000-0x103fffff] [ 0.653524] pcieport 0000:00:00.0: of_irq_parse_pci: failed with rc=-22 [ 0.660132] pcieport 0000:00:00.0: enabling device (0000 -> 0003) [ 0.660306] pcieport 0000:00:00.0: PME: Signaling with IRQ 407 [ 0.660467] pcieport 0000:00:00.0: AER: enabled with IRQ 407 [ 0.660735] j721e-pcie 2910000.pcie: host bridge /bus@100000/pcie@2910000 ranges: [ 0.660752] j721e-pcie 2910000.pcie: IO 0x0018001000..0x0018010fff -> 0x0018001000 [ 0.660762] j721e-pcie 2910000.pcie: MEM 0x0018011000..0x001fffffff -> 0x0018011000 [ 0.660772] j721e-pcie 2910000.pcie: IB MEM 0x0000000000..0xffffffffffff -> 0x0000000000 [ 1.664195] j721e-pcie 2910000.pcie: PCI host bridge to bus 0001:00 [ 1.664201] pci_bus 0001:00: root bus resource [bus 00-ff] [ 1.664206] pci_bus 0001:00: root bus resource [io 0x10000-0x1ffff] (bus address [0x18001000-0x18010fff]) [ 1.664210] pci_bus 0001:00: root bus resource [mem 0x18011000-0x1fffffff] [ 1.664230] pci 0001:00:00.0: [104c:b012] type 01 class 0x060400 [ 1.664235] pci_bus 0001:00: 2-byte config write to 0001:00:00.0 offset 0x4 may corrupt adjacent RW1C bits [ 1.664347] pci 0001:00:00.0: supports D1 [ 1.664350] pci 0001:00:00.0: PME# supported from D0 D1 D3hot [ 1.666280] pci 0001:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring [ 1.666397] pci_bus 0001:01: busn_res: [bus 01-ff] end is updated to 01 [ 1.666410] pci 0001:00:00.0: PCI bridge to [bus 01] [ 1.666462] pcieport 0001:00:00.0: of_irq_parse_pci: failed with rc=-22

Our questions are:

- Is it possible, on Jacinto J784S4, to actually perform read/write accesses to I/O BARs on a PCIe endpoint (FPGA) ?

- If not, is there any hardware or software workaround (device tree, kernel, configuration) to enable this?

- If this is not possible, can you confirm that only memory BARs (MEM) are truly accessible?

Any documentation pointers or detailed explanation about the SoC limitations would be greatly appreciated.

Thank you very much for your help!

Best regards,

K.Luong