Other Parts Discussed in Thread: AM62P, SYSCONFIG

Tool/software:

Hello.

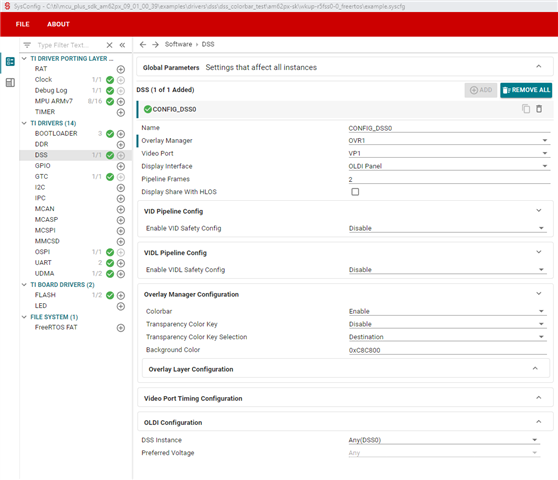

I need to manage a single link LVDS display (4 lanes + clock) from the wakeup R5.

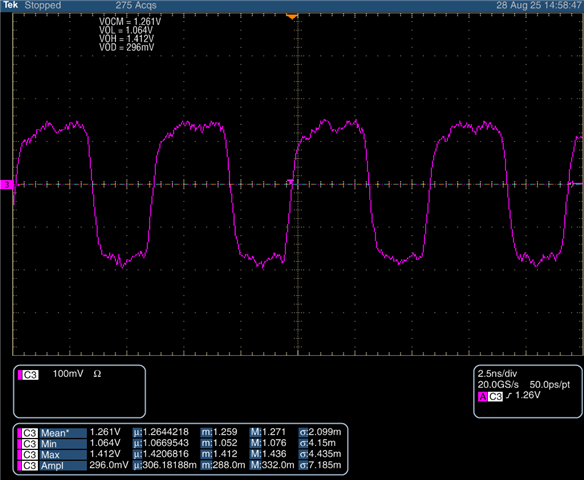

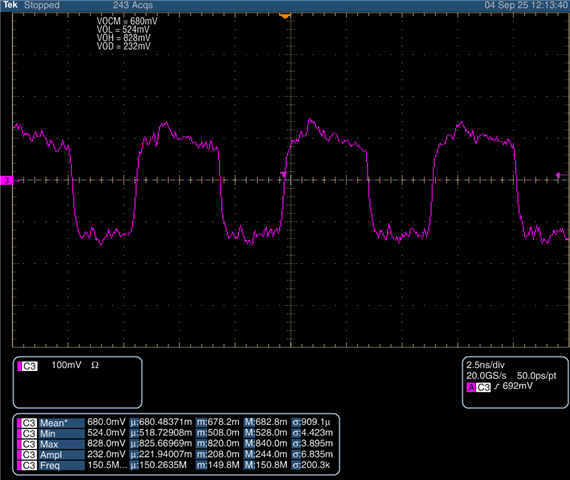

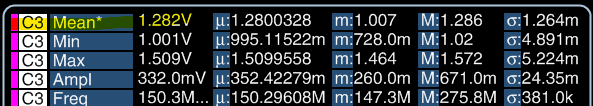

The issue is that when switching to single link (from the syscfg), the LVDS common mode voltage drops to 0.6V

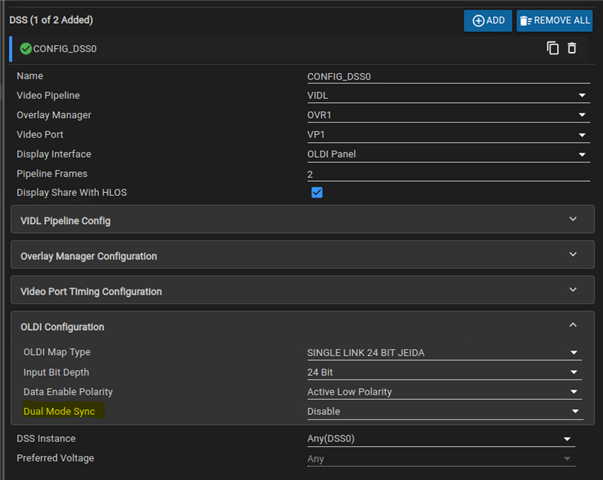

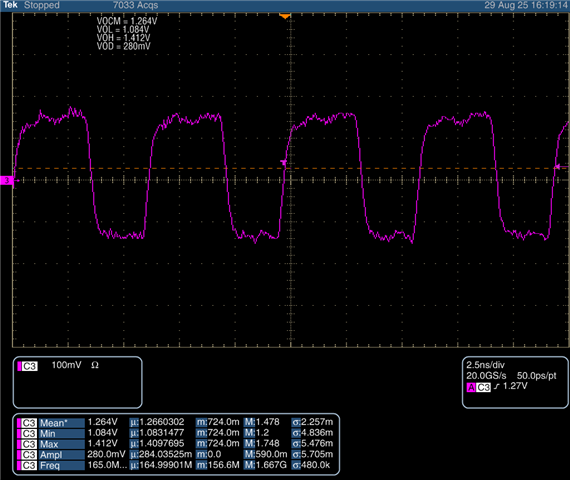

Changing under "OLDI configration" the "Dual Mode" to enable, the LVDS common mode voltage is (as expected) 1.2V.

The datasheet says that the LVDS common mode voltage is 1.125V (min) - 1.375V (max).

Why changing the LVDS configuration to single link drops the Vocm to 0.6V? How to prevent that?

Thank you!

Francesco