Other Parts Discussed in Thread: TCA6424

Tool/software:

Hi,

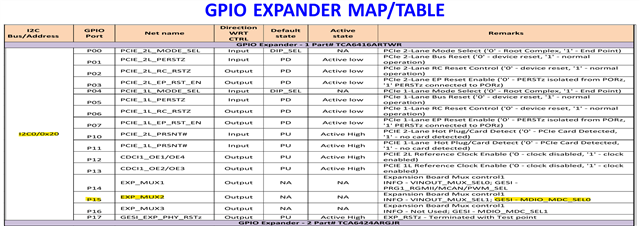

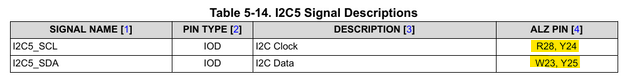

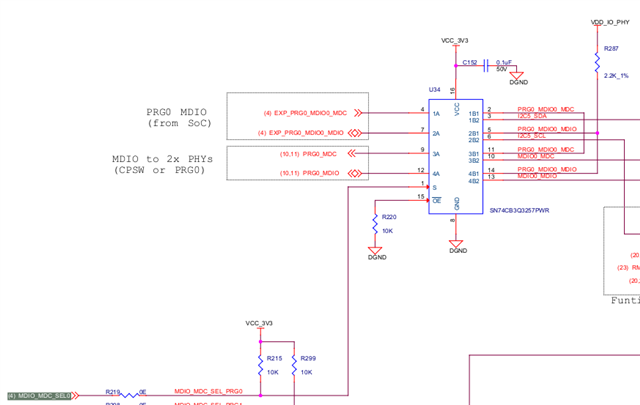

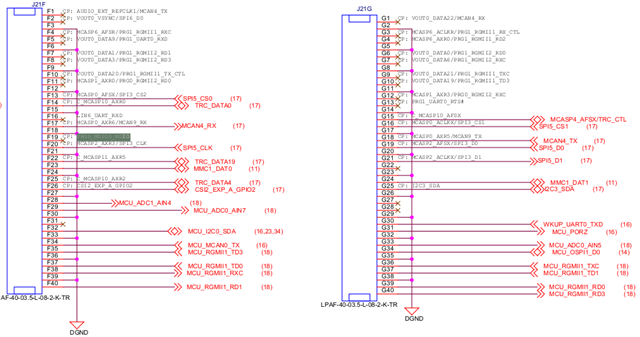

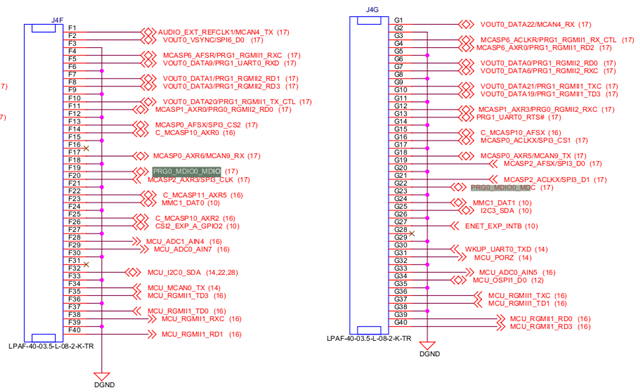

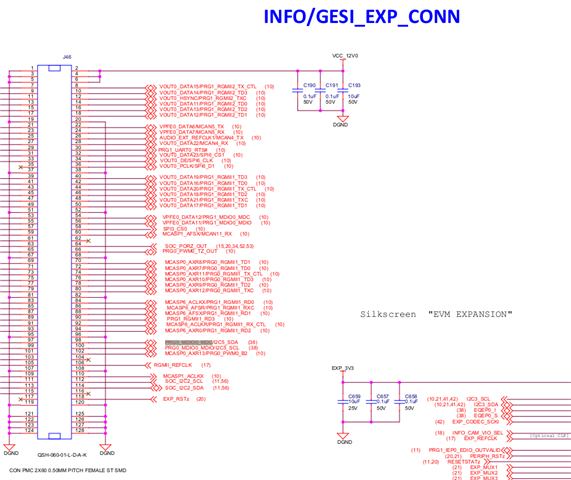

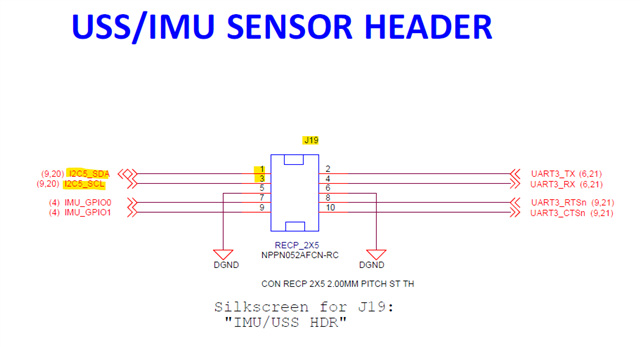

I have set the Pinmux Config to GPIO for Pins(Y25, R28, W23, Y24), as I am not really sure which two out of those four are actually mapped to the J19 connector on GESI Board

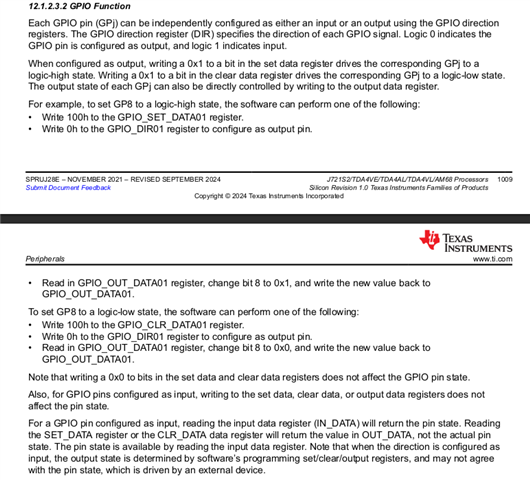

I could see that the registers are configured as expected, and the GPIO output is also updated on the GPIO0_MEM_OUT_DATA01, as well as GPIO0_SET_* and GPIO0_CLR_* registers.

So, my expectation is I should be able to see the I2C5_SCL(R28 or Y24) and I2C_SDA(Y25 or W23) toggle from high to low and low to high, but I don't see any change on the Scope.

I suppose only the *SET* and *OUT* should show the expected output and *CLR* should be opposite to *SET*. If that is how it is supposed to be, then it looks like for some reason SET and CLR instructions are happening at almost next to each other, which makes the pin always stay low.

Could you kindly let me know, if I miss something or how could I get it to work?

I am using,

- J721S2 SOM (PROC118E3)

- GESI Card (PROC084A)

- Jacinto 7 CPB (PROC079A)

- PDK 11.0.0.21

- Baremetal GPIO Blink code is modified accordingly.

Thanks.

Best,

Moses