Other Parts Discussed in Thread: PCA9306, AM6442

Tool/software:

Hi,

I am using AM6204 and would like to clarify on some peripheral input slew rate specification.

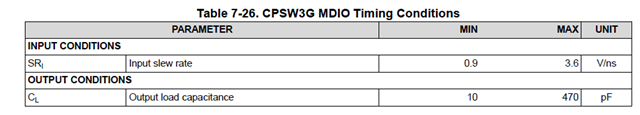

- In my device, the actual measured input slew rate for MDIO is 0.14V/ns, which is not within range of 0.9V/ns ~ 3.6V/ns as specified in Table 7-26. CPSW3G MDIO Timing Conditions. The maximum data rate of MDIO for my application is only 625kHz.

- Is the Input slew rate specification in Table 7-26 applicable to higher data rate e.g. 5MHz only?

- Can i refer to input slew rate in 7.8.6 LVCMOS Electrical Characteristics for my application? E.g. input slew rate specification = 33fV/ns = 0.0206V/ns?

2. For SPI data input, the actual measured input slew rate is 1.45V/ns, which is not within range of 2V/ns ~ 8.5V/ns as specified in Table 7-74. MCSPI Timing Conditions.The maximum data rate of SPI for my application is only 10MHz. Similarly, can i refer to input slew rate in 7.8.6 LVCMOS Electrical Characteristics for my application? E.g. input slew rate specification= 33fV/ns = 0.33V/ns?

3. For Enhanced Capture (ECAP) Input, the actual measured input slew rate is 0.04V/ns, which is not within range of 1V/ns ~ 4V/ns as specified in Table 7-45. ECAP Timing Conditions. The maximum data rate of ECAP for my application is only 1Hz. Similarly, can i refer to input slew rate in 7.8.6 LVCMOS Electrical Characteristics for my application? E.g. input slew rate specification = 3.3MV/s?

4. For GPIOx, in my application the toggling frequency is below 10kHz. shall i refer to the input slew rate in 7.8.6 LVCMOS Electrical Characteristics for my application? E.g. input slew rate = 3.3MV/s?

There is another GPIO timing specification in Table 7-59. GPIO Timing Conditions, is this for high toggling frequency application only? What is value for functional clock period?

5. What are the impacts if the input slew rate specification is not satisfied?