Tool/software:

TDA4VPE custom board

SDK 11.0 linux + freertos

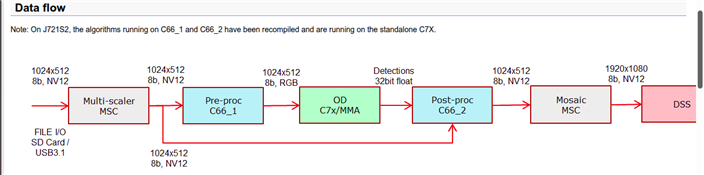

We are currently conducting load pressure tests for the DSP MMA.

By running the app_tidl_od program under the vision_apps directory, we found that only the C7x_1 load was full. According to the datasheet, there are two MMA in the TDA4VPE. Therefore, we ran the second app_tidl_od program and set the TIDLNode node to C7x_2.

However, we found that when running one app_tidl_od, the load on the C7x could reach 100%, but when running the second app_tidl_od, the load on both C7x was 66%. Therefore, we believe that there is resource competition between the two app_tidl_od, which led to the inability of the C7x MMA to operate at full capacity.

And we would like to know if there is any way to obtain the load of MMA, or we can simply assume that when the C7x load is 100%, then the load of MMA is also 100%.

This is the log of running the first app_tidl_od.

root@tda4ape-dv:/hirain/data/debug_od/debug_hirain# ./vx_app_tidl_od.out.core_id --cfg app_od_0.cfg

APP: Init ... !!!

63.631683 s: MEM: Init ... !!!

63.631760 s: MEM: Initialized DMA HEAP (fd=5) !!!

63.631931 s: MEM: Init ... Done !!!

63.631951 s: IPC: Init ... !!!

63.654297 s: IPC: Init ... Done !!!

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

63.664002 s: GTC Frequency = 200 MHz

APP: Init ... Done !!!

63.665572 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_ERROR

63.665606 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_WARNING

63.665624 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_INFO

63.667406 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-0

63.667747 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-1

63.667910 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-2

63.668041 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-3

63.668059 s: VX_ZONE_INFO: [tivxInitLocal:202] Initialization Done !!!

63.668149 s: VX_ZONE_INFO: Globally Disabled VX_ZONE_INFO

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice: app_tidl_od: Iteration 0 of 1000000000 ... Done.

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice: p

Summary of CPU load,

====================

CPU: mpu1_0: TOTAL LOAD = 19.53 % ( HWI = 0.69 %, SWI = 0.11 % )

CPU: mcu2_0: TOTAL LOAD = 7. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_1: TOTAL LOAD = 2. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu3_0: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu3_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu4_0: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu4_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_1: TOTAL LOAD = 98. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_2: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_3: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

HWA performance statistics,

===========================

HWA: MSC0: LOAD = 65.54 % ( 429 MP/s )

DDR performance statistics,

===========================

DDR: READ BW: AVG = 2175 MB/s, PEAK = 4205 MB/s

DDR: WRITE BW: AVG = 1038 MB/s, PEAK = 2378 MB/s

DDR: TOTAL BW: AVG = 3213 MB/s, PEAK = 6583 MB/s

Detailed CPU performance/memory statistics,

===========================================

67.988204 s: DDR_SHARED_MEM: Alloc's: 30 alloc's of 17301760 bytes

67.988222 s: DDR_SHARED_MEM: Free's : 0 free's of 0 bytes

67.988235 s: DDR_SHARED_MEM: Open's : 30 allocs of 17301760 bytes

CPU: mcu2_0: TASK: FREERTOS_TA: 1.24 %

CPU: mcu2_0: TASK: lwIP main l: 0. 0 %

CPU: mcu2_0: TASK: IPC_RX: 0.17 %

CPU: mcu2_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CPU_0: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1NF: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1LDC: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1MSC1: 2.63 %

CPU: mcu2_0: TASK: TIVX_V1MSC2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1VISS: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT5: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT6: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT7: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT8: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT9: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT10: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT11: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT12: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1FC: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: HEAP: DDR_LOCAL_MEM: size = 6291456 B, free = 6282240 B ( 99 % unused)

CPU: mcu2_0: HEAP: L3_MEM: size = 262144 B, free = 261888 B ( 99 % unused)

CPU: mcu2_0: HEAP: DDR_CACHE_WT_ME: size = 2097152 B, free = 2096896 B ( 99 % unused)

CPU: mcu2_1: TASK: FREERTOS_TA: 1.30 %

CPU: mcu2_1: TASK: IPC_RX: 0. 0 %

CPU: mcu2_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_1: TASK: TIVX_CPU_1: 0. 0 %

CPU: mcu2_1: TASK: TIVX_SDE: 0. 0 %

CPU: mcu2_1: TASK: TIVX_DOF: 0. 0 %

CPU: mcu2_1: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu2_1: HEAP: L3_MEM: size = 262144 B, free = 262144 B (100 % unused)

CPU: mcu3_0: TASK: FREERTOS_TA: 0.85 %

CPU: mcu3_0: TASK: IPC_RX: 0. 0 %

CPU: mcu3_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu3_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu3_0: TASK: TIVX_MCU3_0: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu3_1: TASK: FREERTOS_TA: 0.76 %

CPU: mcu3_1: TASK: IPC_RX: 0. 0 %

CPU: mcu3_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu3_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu3_1: TASK: TIVX_MCU3_1: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu4_0: TASK: FREERTOS_TA: 0.32 %

CPU: mcu4_0: TASK: IPC_RX: 0. 0 %

CPU: mcu4_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu4_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu4_0: TASK: TIVX_MCU4_0: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2NF: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2LDC: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2MSC1: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2MSC2: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2VISS: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2FC: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: HEAP: DDR_LOCAL_MEM: size = 6291456 B, free = 6287360 B ( 99 % unused)

CPU: mcu4_0: HEAP: L3_MEM: size = 524288 B, free = 524288 B (100 % unused)

CPU: mcu4_0: HEAP: DDR_CACHE_WT_ME: size = 2097152 B, free = 2096896 B ( 99 % unused)

CPU: mcu4_1: TASK: FREERTOS_TA: 0.25 %

CPU: mcu4_1: TASK: IPC_RX: 0. 0 %

CPU: mcu4_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu4_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu4_1: TASK: TIVX_MCU4_1: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: c7x_1: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_1: TASK: IPC_RX: 0.31 %

CPU: c7x_1: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_1: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P1: 98.80 %

CPU: c7x_1: TASK: TIVX_C71_P2: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P3: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P4: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P5: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P6: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P7: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P8: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 127003136 B ( 94 % unused)

CPU: c7x_1: HEAP: L3_MEM: size = 3145728 B, free = 131072 B ( 4 % unused)

CPU: c7x_1: HEAP: L2_MEM: size = 458752 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: L1_MEM: size = 16384 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 126410257 B ( 94 % unused)

CPU: c7x_1: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 130656255 B ( 97 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134197120 B ( 99 % unused)

CPU: c7x_2: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_2: TASK: IPC_RX: 0. 0 %

CPU: c7x_2: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_2: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P1: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P2: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P3: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P4: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P5: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P6: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P7: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P8: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 134213120 B ( 99 % unused)

CPU: c7x_2: HEAP: L3_MEM: size = 3145728 B, free = 3145728 B (100 % unused)

CPU: c7x_2: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_2: HEAP: L1_MEM: size = 16384 B, free = 16384 B (100 % unused)

CPU: c7x_2: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_2: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_2: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_3: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_3: TASK: IPC_RX: 0. 0 %

CPU: c7x_3: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_3: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P1: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P2: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P3: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P4: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P5: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P6: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P7: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P8: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 134213120 B ( 99 % unused)

CPU: c7x_3: HEAP: L3_MEM: size = 3145728 B, free = 3145728 B (100 % unused)

CPU: c7x_3: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_3: HEAP: L1_MEM: size = 16384 B, free = 16384 B (100 % unused)

CPU: c7x_3: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_3: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_3: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134217728 B (100 % unused)

GRAPH: OpenVxGraph (#nodes = 5, #executions = 953)

NODE: VPAC_MSC1: scaler_node: avg = 1509 usecs, min/max = 1397 / 1631 usecs, #executions = 953

NODE: MPU-0: PreProcNode: avg = 451 usecs, min/max = 433 / 902 usecs, #executions = 953

NODE: DSP_C7-1: tidl_node: avg = 4186 usecs, min/max = 4150 / 4511 usecs, #executions = 953

NODE: MPU-0: post_proc_node: avg = 544 usecs, min/max = 440 / 1076 usecs, #executions = 953

NODE: VPAC_MSC1: mosaic_node: avg = 1628 usecs, min/max = 1549 / 9736 usecs, #executions = 953

PERF: FILEIO: avg = 1690 usecs, min/max = 1448 / 5821 usecs, #executions = 959

PERF: TOTAL: avg = 4233 usecs, min/max = 2005 / 12121 usecs, #executions = 958

PERF: TOTAL: 236.23 FPS

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice:

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice:

This is the log of running the second app_tidl_od.

root@tda4ape-dv:/hirain/data/debug_od/debug_hirain# ./vx_app_tidl_od.out.core_id --cfg app_od_1.cfg

APP: Init ... !!!

96.134879 s: MEM: Init ... !!!

96.135012 s: MEM: Initialized DMA HEAP (fd=5) !!!

96.135222 s: MEM: Init ... Done !!!

96.135247 s: IPC: Init ... !!!

96.159754 s: IPC: Init ... Done !!!

REMOTE_SERVICE: Init ... !!!

REMOTE_SERVICE: Init ... Done !!!

96.172504 s: GTC Frequency = 200 MHz

APP: Init ... Done !!!

96.172632 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_ERROR

96.172675 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_WARNING

96.172689 s: VX_ZONE_INFO: Globally Enabled VX_ZONE_INFO

96.173865 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-0

96.174305 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-1

96.174738 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-2

96.174878 s: VX_ZONE_INFO: [tivxPlatformCreateTargetId:169] Added target MPU-3

96.174899 s: VX_ZONE_INFO: [tivxInitLocal:202] Initialization Done !!!

96.174926 s: VX_ZONE_INFO: Globally Disabled VX_ZONE_INFO

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice: app_tidl_od: Iteration 0 of 1000000000 ... Done.

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice: p

Summary of CPU load,

====================

CPU: mpu1_0: TOTAL LOAD = 29.74 % ( HWI = 0.98 %, SWI = 0. 9 % )

CPU: mcu2_0: TOTAL LOAD = 45. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu2_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu3_0: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu3_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu4_0: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: mcu4_1: TOTAL LOAD = 1. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_1: TOTAL LOAD = 98. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_2: TOTAL LOAD = 64. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

CPU: c7x_3: TOTAL LOAD = 0. 0 % ( HWI = 0. 0 %, SWI = 0. 0 % )

HWA performance statistics,

===========================

HWA: MSC0: LOAD = 82.93 % ( 539 MP/s )

DDR performance statistics,

===========================

DDR: READ BW: AVG = 2758 MB/s, PEAK = 52782 MB/s

DDR: WRITE BW: AVG = 1335 MB/s, PEAK = 23918 MB/s

DDR: TOTAL BW: AVG = 4093 MB/s, PEAK = 76700 MB/s

Detailed CPU performance/memory statistics,

===========================================

98.733109 s: DDR_SHARED_MEM: Alloc's: 30 alloc's of 17301760 bytes

98.733132 s: DDR_SHARED_MEM: Free's : 0 free's of 0 bytes

98.733147 s: DDR_SHARED_MEM: Open's : 30 allocs of 17301760 bytes

CPU: mcu2_0: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu2_0: TASK: lwIP main l: 0. 0 %

CPU: mcu2_0: TASK: IPC_RX: 2.42 %

CPU: mcu2_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CPU_0: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1NF: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1LDC: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1MSC1: 35.99 %

CPU: mcu2_0: TASK: TIVX_V1MSC2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1VISS: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT5: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT6: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT7: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT8: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT9: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT10: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT11: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CAPT12: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DISP2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX: 0. 0 %

CPU: mcu2_0: TASK: TIVX_CSITX2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M1: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M2: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M3: 0. 0 %

CPU: mcu2_0: TASK: TIVX_DPM2M4: 0. 0 %

CPU: mcu2_0: TASK: TIVX_V1FC: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_0: HEAP: DDR_LOCAL_MEM: size = 6291456 B, free = 6277120 B ( 99 % unused)

CPU: mcu2_0: HEAP: L3_MEM: size = 262144 B, free = 261888 B ( 99 % unused)

CPU: mcu2_0: HEAP: DDR_CACHE_WT_ME: size = 2097152 B, free = 2096896 B ( 99 % unused)

CPU: mcu2_1: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu2_1: TASK: IPC_RX: 0. 0 %

CPU: mcu2_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu2_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu2_1: TASK: TIVX_CPU_1: 0. 0 %

CPU: mcu2_1: TASK: TIVX_SDE: 0. 0 %

CPU: mcu2_1: TASK: TIVX_DOF: 0. 0 %

CPU: mcu2_1: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu2_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu2_1: HEAP: L3_MEM: size = 262144 B, free = 262144 B (100 % unused)

CPU: mcu3_0: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu3_0: TASK: IPC_RX: 0. 0 %

CPU: mcu3_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu3_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu3_0: TASK: TIVX_MCU3_0: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_0: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu3_1: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu3_1: TASK: IPC_RX: 0. 0 %

CPU: mcu3_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu3_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu3_1: TASK: TIVX_MCU3_1: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu3_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: mcu4_0: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu4_0: TASK: IPC_RX: 0. 0 %

CPU: mcu4_0: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu4_0: TASK: LOAD_TEST: 0. 0 %

CPU: mcu4_0: TASK: TIVX_MCU4_0: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2NF: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2LDC: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2MSC1: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2MSC2: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2VISS: 0. 0 %

CPU: mcu4_0: TASK: TIVX_V2FC: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_0: HEAP: DDR_LOCAL_MEM: size = 6291456 B, free = 6287360 B ( 99 % unused)

CPU: mcu4_0: HEAP: L3_MEM: size = 524288 B, free = 524288 B (100 % unused)

CPU: mcu4_0: HEAP: DDR_CACHE_WT_ME: size = 2097152 B, free = 2096896 B ( 99 % unused)

CPU: mcu4_1: TASK: FREERTOS_TA: 0. 0 %

CPU: mcu4_1: TASK: IPC_RX: 0. 0 %

CPU: mcu4_1: TASK: REMOTE_SRV: 0. 0 %

CPU: mcu4_1: TASK: LOAD_TEST: 0. 0 %

CPU: mcu4_1: TASK: TIVX_MCU4_1: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: mcu4_1: HEAP: DDR_LOCAL_MEM: size = 8388608 B, free = 8388352 B ( 99 % unused)

CPU: c7x_1: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_1: TASK: IPC_RX: 0.31 %

CPU: c7x_1: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_1: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P1: 97.10 %

CPU: c7x_1: TASK: TIVX_C71_P2: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P3: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P4: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P5: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P6: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P7: 0. 0 %

CPU: c7x_1: TASK: TIVX_C71_P8: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_1: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 127003136 B ( 94 % unused)

CPU: c7x_1: HEAP: L3_MEM: size = 3145728 B, free = 131072 B ( 4 % unused)

CPU: c7x_1: HEAP: L2_MEM: size = 458752 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: L1_MEM: size = 16384 B, free = 0 B ( 0 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 126410257 B ( 94 % unused)

CPU: c7x_1: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 130656255 B ( 97 % unused)

CPU: c7x_1: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134197120 B ( 99 % unused)

CPU: c7x_2: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_2: TASK: IPC_RX: 0.21 %

CPU: c7x_2: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_2: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P1: 65.15 %

CPU: c7x_2: TASK: TIVX_C72_P2: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P3: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P4: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P5: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P6: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P7: 0. 0 %

CPU: c7x_2: TASK: TIVX_C72_P8: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_2: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 126998784 B ( 94 % unused)

CPU: c7x_2: HEAP: L3_MEM: size = 3145728 B, free = 131072 B ( 4 % unused)

CPU: c7x_2: HEAP: L2_MEM: size = 458752 B, free = 0 B ( 0 % unused)

CPU: c7x_2: HEAP: L1_MEM: size = 16384 B, free = 0 B ( 0 % unused)

CPU: c7x_2: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 126410257 B ( 94 % unused)

CPU: c7x_2: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 130656255 B ( 97 % unused)

CPU: c7x_2: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134197120 B ( 99 % unused)

CPU: c7x_3: TASK: FREERTOS_TA: 0. 0 %

CPU: c7x_3: TASK: IPC_RX: 0. 0 %

CPU: c7x_3: TASK: REMOTE_SRV: 0. 0 %

CPU: c7x_3: TASK: LOAD_TEST: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P1: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P2: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P3: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P4: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P5: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P6: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P7: 0. 0 %

CPU: c7x_3: TASK: TIVX_C73_P8: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_RX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: TASK: IPC_TEST_TX: 0. 0 %

CPU: c7x_3: HEAP: DDR_LOCAL_MEM: size = 134217728 B, free = 134213120 B ( 99 % unused)

CPU: c7x_3: HEAP: L3_MEM: size = 3145728 B, free = 3145728 B (100 % unused)

CPU: c7x_3: HEAP: L2_MEM: size = 458752 B, free = 458752 B (100 % unused)

CPU: c7x_3: HEAP: L1_MEM: size = 16384 B, free = 16384 B (100 % unused)

CPU: c7x_3: HEAP: DDR_SCRATCH_MEM: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_3: HEAP: DDR_NON_CACHE_M: size = 134217728 B, free = 134217728 B (100 % unused)

CPU: c7x_3: HEAP: DDR_SCRATCH_NON: size = 134217728 B, free = 134217728 B (100 % unused)

GRAPH: OpenVxGraph (#nodes = 5, #executions = 339)

NODE: VPAC_MSC1: scaler_node: avg = 1524 usecs, min/max = 1450 / 1620 usecs, #executions = 339

NODE: MPU-0: PreProcNode: avg = 530 usecs, min/max = 492 / 1456 usecs, #executions = 339

NODE: DSP_C7-2: tidl_node: avg = 4363 usecs, min/max = 4303 / 4704 usecs, #executions = 339

NODE: MPU-0: post_proc_node: avg = 636 usecs, min/max = 460 / 1298 usecs, #executions = 339

NODE: VPAC_MSC1: mosaic_node: avg = 1718 usecs, min/max = 1574 / 9693 usecs, #executions = 339

PERF: FILEIO: avg = 2009 usecs, min/max = 1674 / 3134 usecs, #executions = 343

PERF: TOTAL: avg = 6747 usecs, min/max = 3221 / 14981 usecs, #executions = 342

PERF: TOTAL: 148.21 FPS

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice:

=========================

TIDL Demo - Object Detection

=========================

p: Print performance statistics

x: Exit

Enter Choice:

When the second app_tidl_od starts running, the load of the first app_tidl_od drops from 100% to around 60%, which is the same as that of the second one. The frame rate also decreases from 240 to around 140, which is also the same as that of the second one.

How should we modify the code in order to ensure that both the DSP and MMA are operating at full capacity?