Tool/software:

Hi Team,

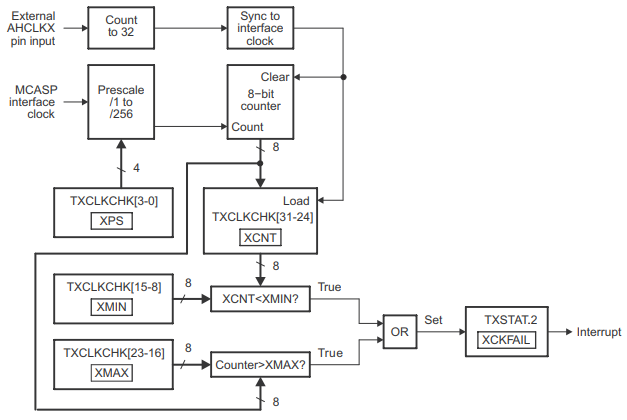

I tried retrieving the XCNT value programmatically, but I’m not quite sure how the value is actually calculated.

Could someone explain the calculation method used to derive the XCNT value?

Here’s the environment I’m working with:

- External AHCLKX: 24.5 MHz

- Sampling frequency: 48,000 Hz

- Frame period: 32 fs

I’m using the following code to read the XCNT value:

#define MCASP_XCLKCHK_OFFSET 0x00C8

volatile uint32_t *MCASP1_XCLKCHK = (volatile uint32_t *)(CSL_MCASP1_CFG_BASE + MCASP_XCLKCHK_OFFSET);

#define XCKCHK_MAX 90

#define XCKCHK_MIN 70

void init_mcasp1_xclkchk()

{

uint32_t val = CSL_REG32_RD(MCASP1_XCLKCHK);

// clear

val &= ((0x00 << 16) | (0x00 << 8));

// Setting MAX/MIN

val |= (XCKCHK_MAX << 16);

val |= (XCKCHK_MIN << 8);

// RPS (McASP system clock divided by 4)

val |= (2 << 0);

// write

CSL_REG32_WR(MCASP1_XCLKCHK, val);

}

void chk_mcasp1_xcnt()

{

uint32_t xcnt = (CSL_REG32_RD(MCASP1_XCLKCHK) >> 24) & 0xFF;

uint32_t xmax = (CSL_REG32_RD(MCASP1_XCLKCHK) >> 16) & 0xFF;

uint32_t xmin = (CSL_REG32_RD(MCASP1_XCLKCHK) >> 8) & 0xFF;

DebugP_log("[MCASP1]XCNT: %3u | XMAX: %3u | XMIN: %3u\r\n", xcnt, xmax, xmin);

}

void clock_check_main(void *args)

{

while(true) {

chk_mcasp1_xcnt();

DebugP_log("-----------------------------------------\r\n");

vTaskDelay(pdMS_TO_TICKS(1*1000));

}

}

Here’s a snippet of the output:

[MCASP1]XCNT: 82 | XMAX: 90 | XMIN: 70 ----------------------------------------- [MCASP1]XCNT: 81 | XMAX: 90 | XMIN: 70 ----------------------------------------- [MCASP1]XCNT: 82 | XMAX: 90 | XMIN: 70 ----------------------------------------- [MCASP1]XCNT: 82 | XMAX: 90 | XMIN: 70 -----------------------------------------