Tool/software:

Hello,

Good day!

There is customer's issue, could you help? Thank you so much.

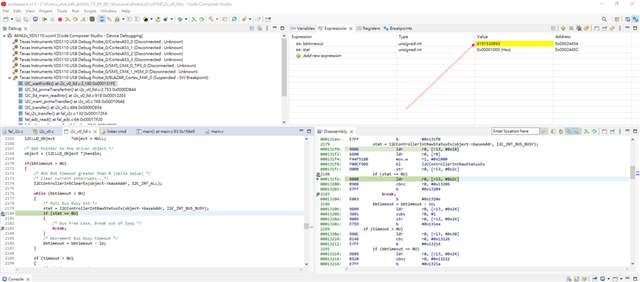

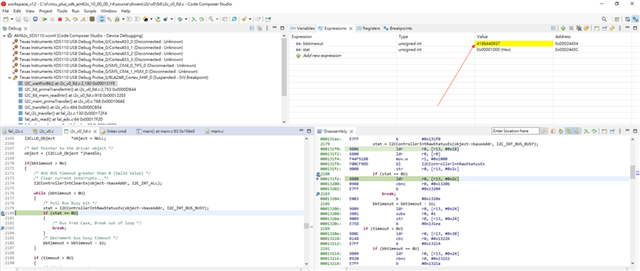

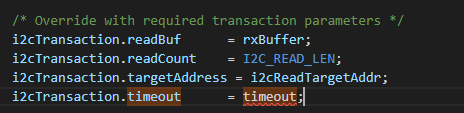

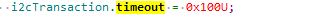

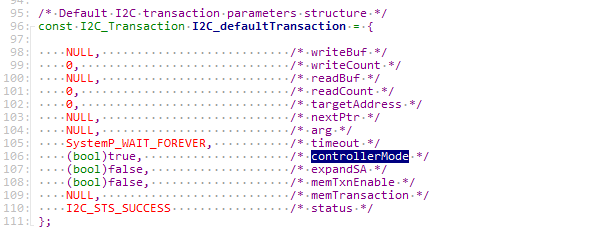

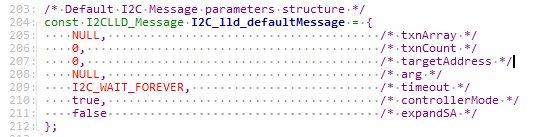

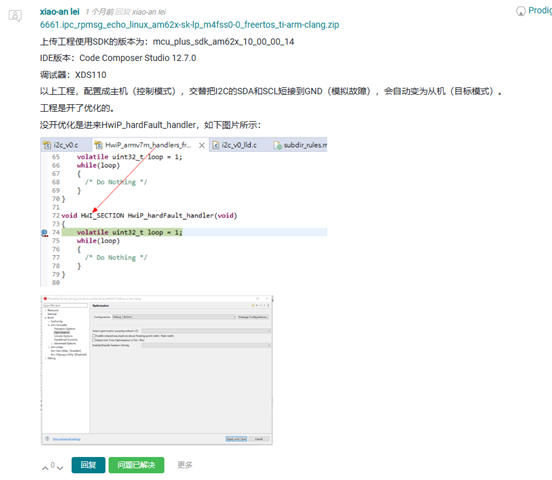

Preface: External watchdog is used to feed dogs in RTOS tasks. During troubleshooting the issue of abnormal reset, it was found that I2C communication abnormalities can cause reset. The following is detailed information on simulation debugging.

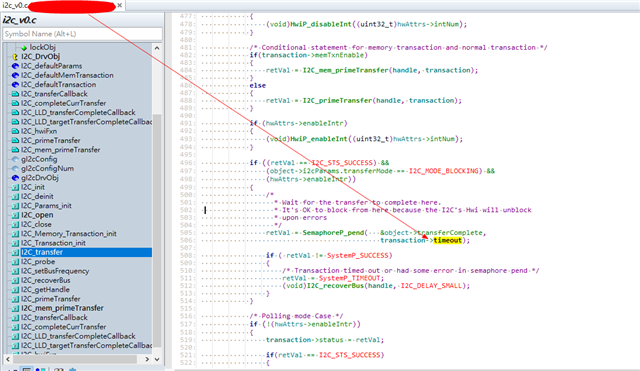

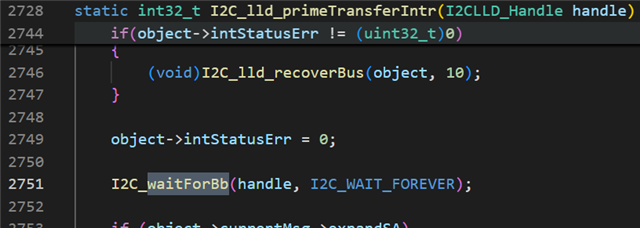

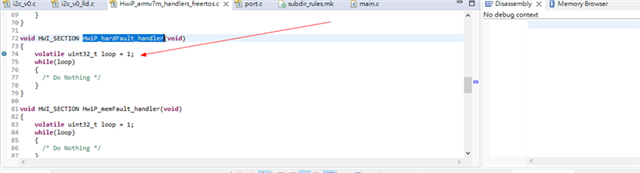

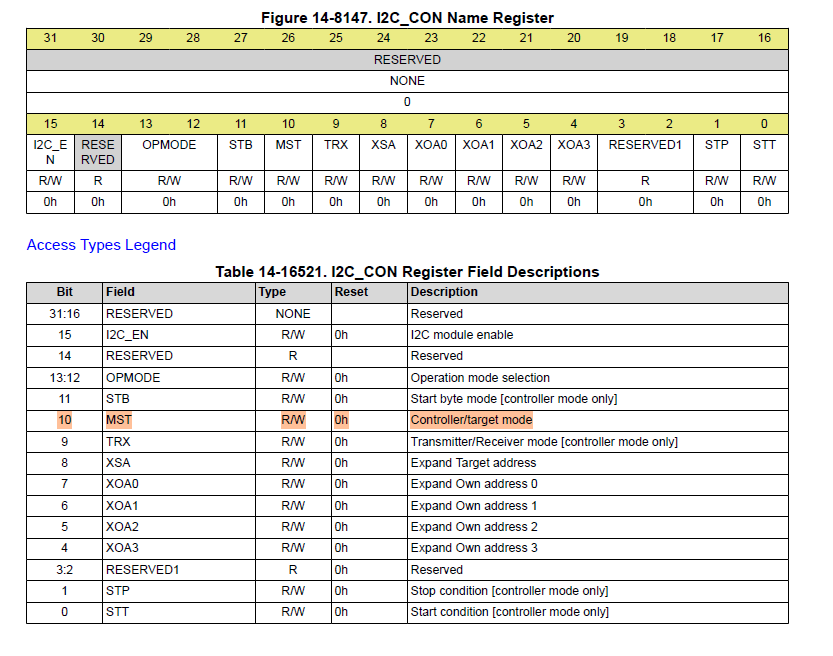

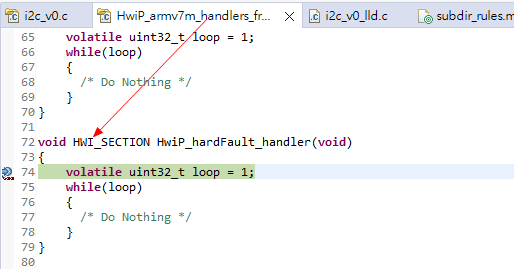

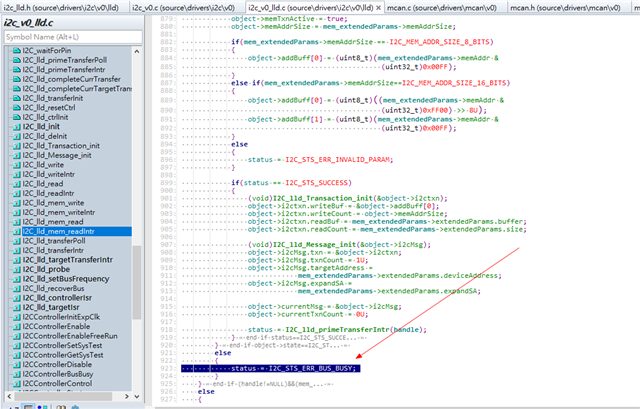

I2C communication exception caused program crash, interrupt continues to I2C_lld_targetIsr, unable to enter task function, all tasks starved to death.

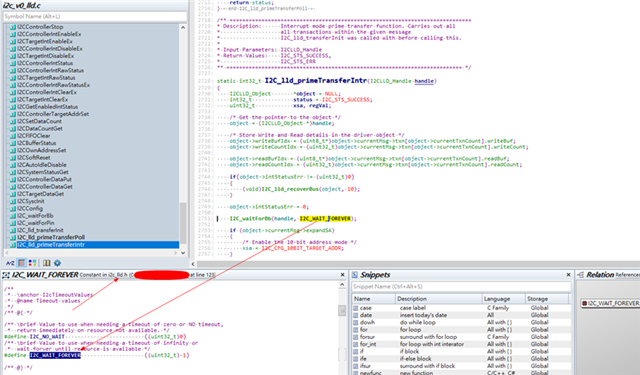

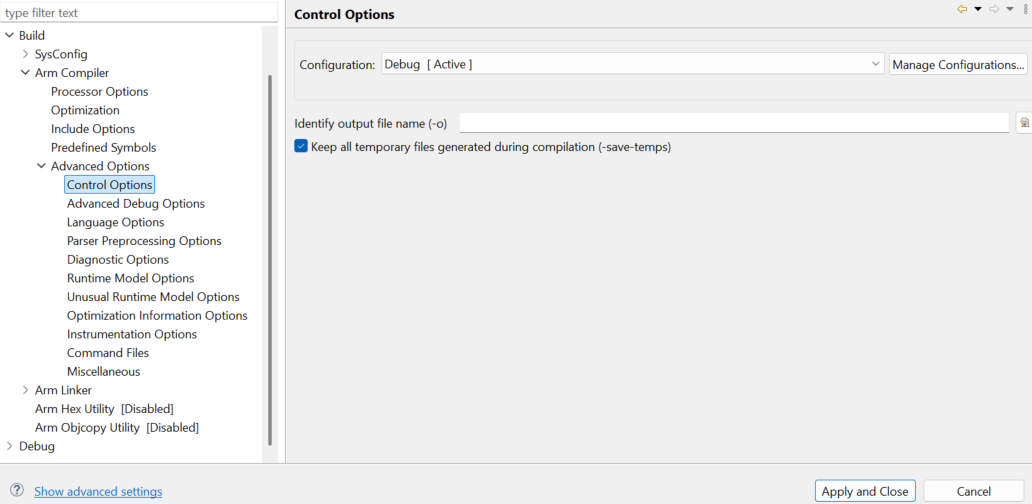

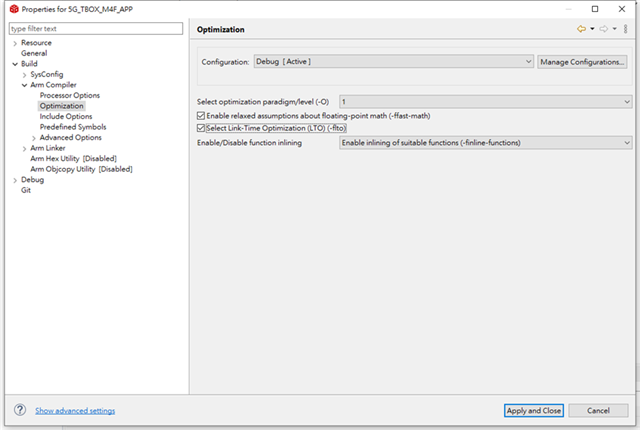

I found that enabling the optimization feature in the compiler leads to the above issues. The compiler optimization settings are shown in the picture:

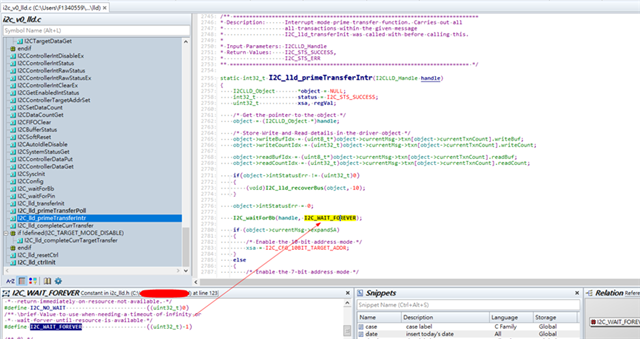

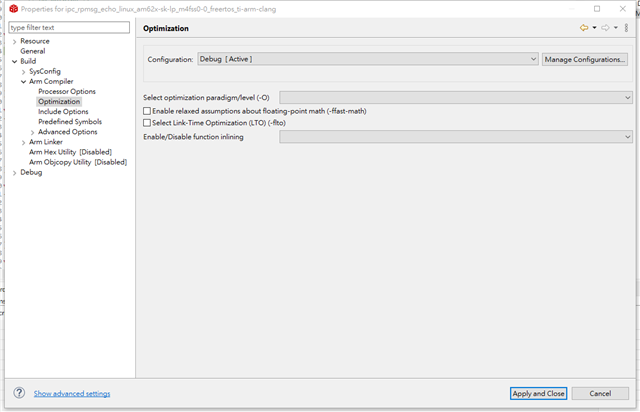

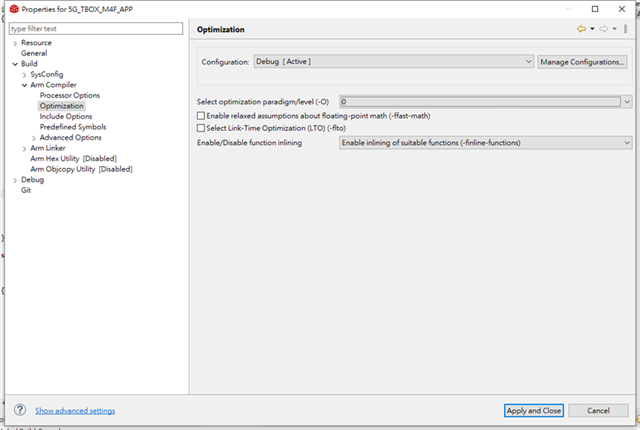

After turning off the compiler optimization, the issue did not reoccur. The compiler settings for this are shown in the picture:

However, if our project does not enable optimization, the stack will overflow. Is there any solution to this?