Tool/software:

Hi TI Team,

We are currently designing a custom board using the AM62L processor with LPDDR4 memory and have noticed discrepancies in the impedance requirements for LPDDR4 signal routing.

-

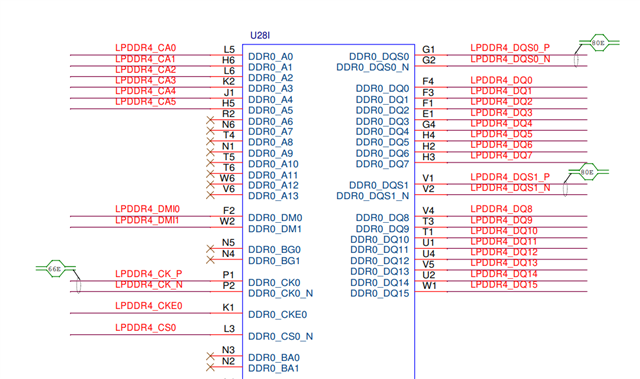

In the EVM schematic, the specified impedance is:

-

66Ω for

LPDDR4_CK_P/N -

80Ω for

LPDDR4_DQSx_P/N

-

-

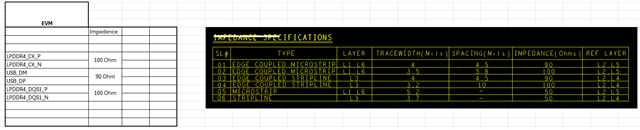

However, in the EVM layout, the routing follows:

-

100Ω differential

-

50Ω single-ended

-

-

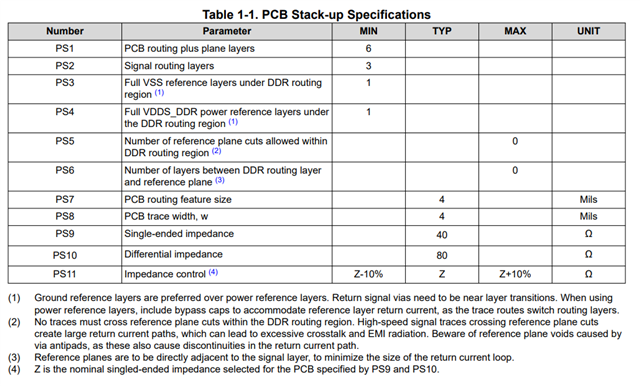

In the LPDDR4 Routing Guidelines document, the recommendation is:

-

80Ω differential

-

40Ω single-ended

-

We have attached screenshots from the schematic, layout, and the routing guideline document for your reference.

Could you please confirm which impedance values we should follow for our custom board to ensure signal integrity.

Looking forward to your guidance.

Best regards,

Jaydip