Other Parts Discussed in Thread: TMS320F28335,

Tool/software:

Dear Sir,

I am an engineer from Kangni Electronics Company in Nanjing, China.We found the following issues when using AM3352 and TMS320F28335 for SPI communication.

The control board DSP TMS320F28335 and communication board AM3352 are connected through SPI cable plug connection, ARM as the master device and DSP as the slave device.

During the use of the project, there may be occasional power on situations where SPI cannot communicate, SPI Flashing communication failure, or persistent communication issues.

The Linux u-boot for AM3352 is u-boot-2013.01.01-psp06.00.00.00.

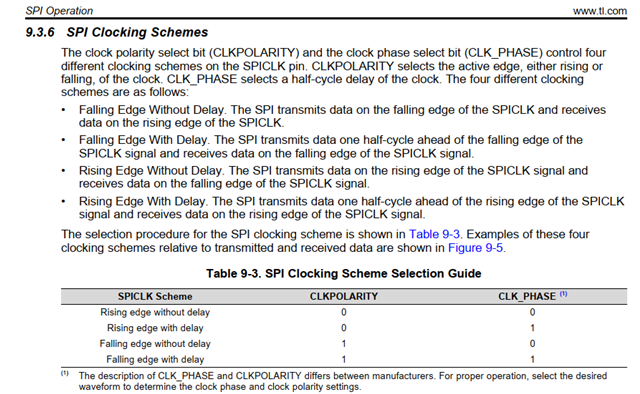

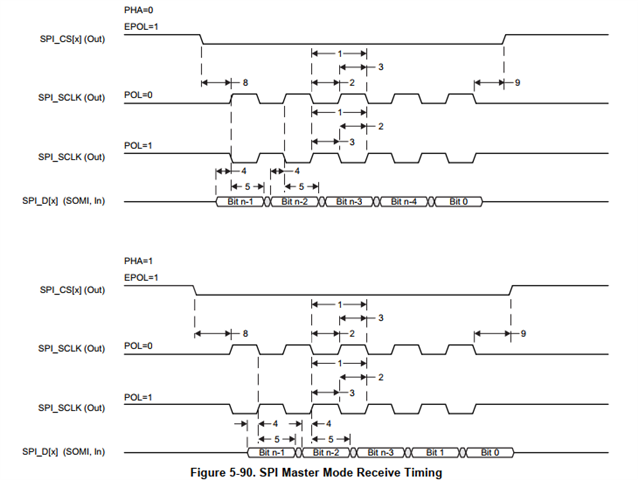

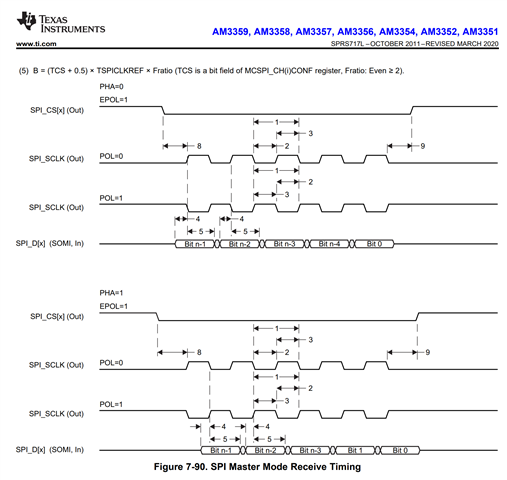

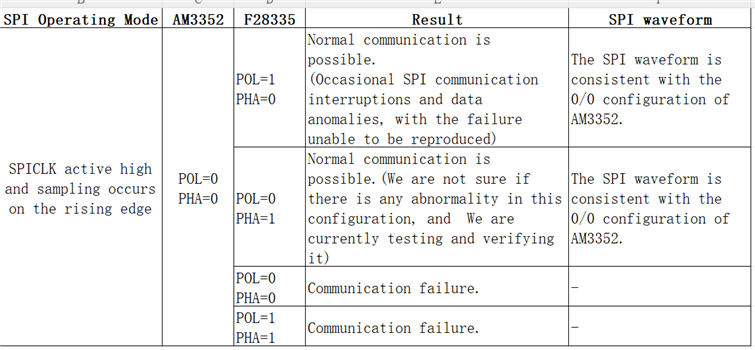

1. Why are the clock timings for data transmission and reception different in the manuals of ARM and DSP chips with the same SPI polarity/phase configuration?

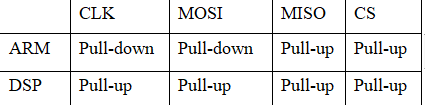

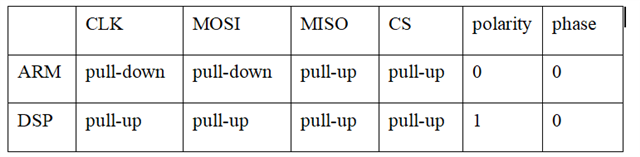

2. The current configuration is as follows, please check if it is correct? What is the standard configuration?

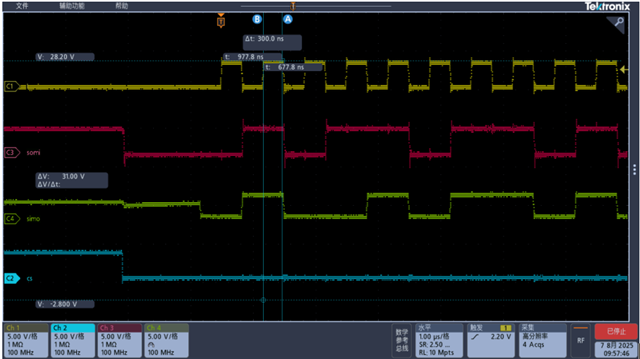

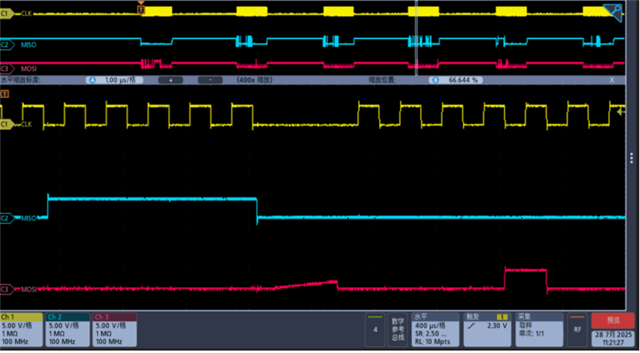

3.The SPI waveform of the current configuration is as follows. Please check if there are any abnormalities? What is the standard waveform?

Thank you!

zhou zhou