Part Number: AM62P-Q1

Tool/software:

Hello,

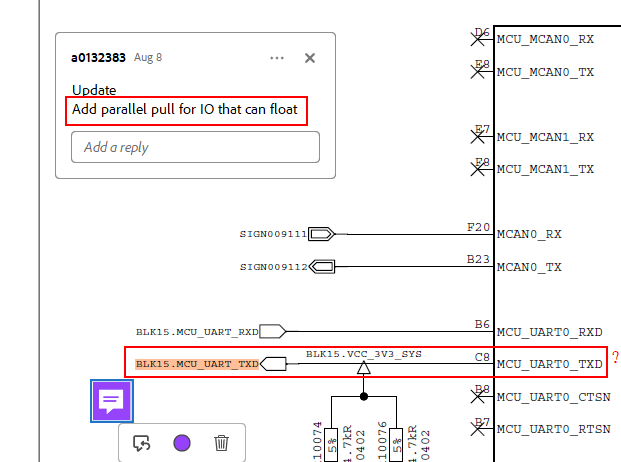

as below show, when our application schematic reviewed by TI, some comments given, but here i'm not understand very clearly about "Add parallel pull for IO that can float"? does means if this PIN not used in application, we need to add external pull up/down for this PIN? and no external pull needed if this PIN used, right? thanks!