Tool/software:

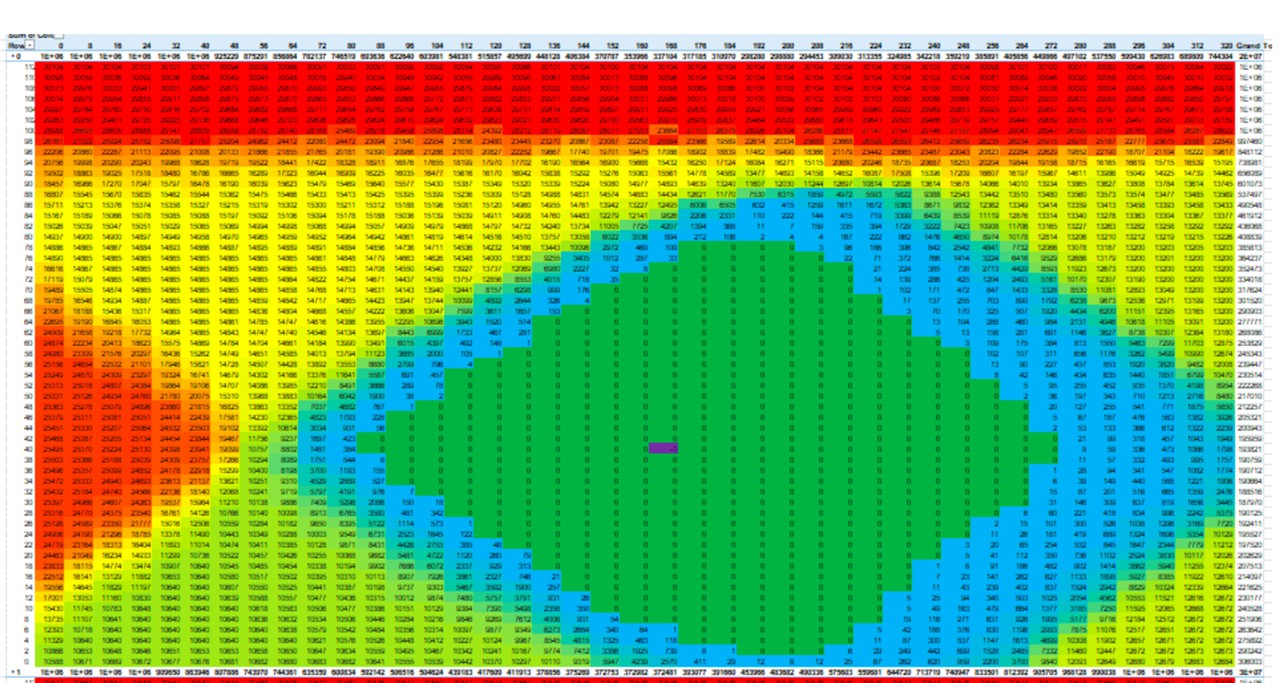

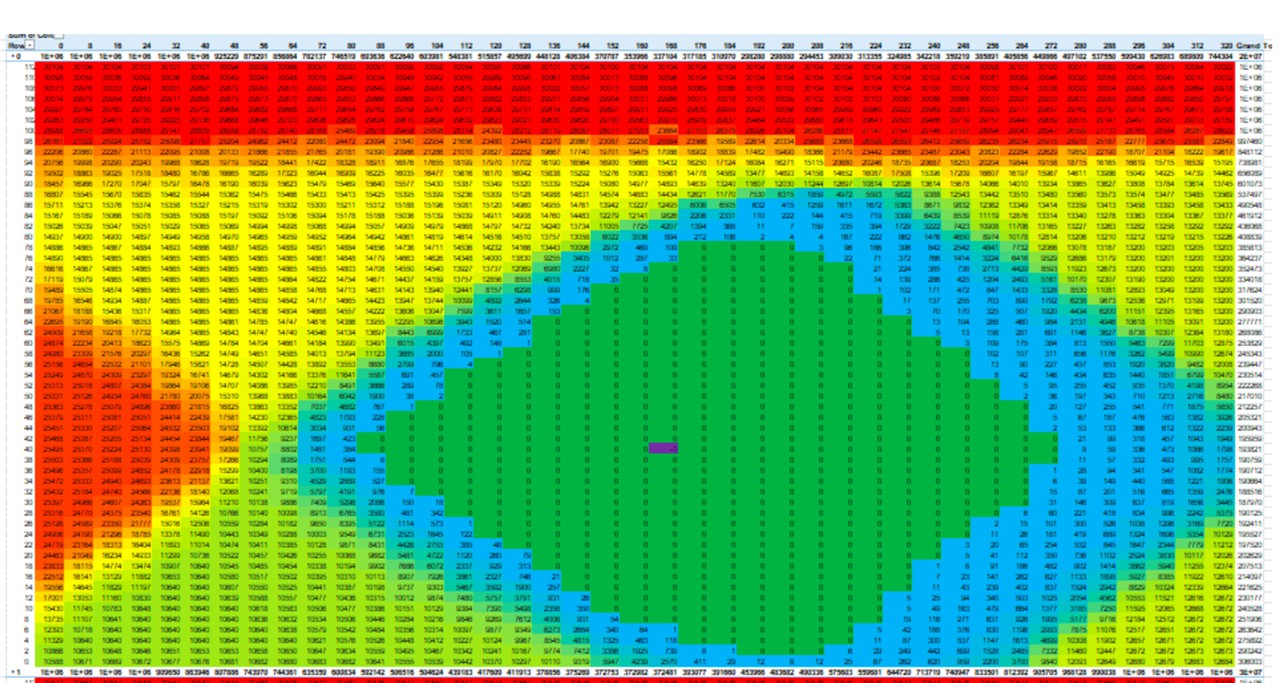

Could you please explain the details of the plot below: (a) what do vertical and horizontal axis mean? (b) what is the color coding criteria? (c) how the numerical ratings are obtained? Any other comments? -- thank you!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Could you please explain the details of the plot below: (a) what do vertical and horizontal axis mean? (b) what is the color coding criteria? (c) how the numerical ratings are obtained? Any other comments? -- thank you!

I answered my own question consulting the user's manual (DDR Margin Analysis Tool User's Manual). Only the first introductory page is completed - when will the remaining information become available?

Thank you!

Greetings Lenio,

Gentle FYI, this plot is from a version of the tool for Jacinto devices. The version that supports AM62P is here: https://www.ti.com/tool/download/DDR-MARGIN-FW/

That being said, they both function essentially the same, though the output itself differs slightly on if this picture is from a read eye vs a write eye:

1) Each vertical tick is a different DQ VREF setting in either the DDR IP or DRAM and these settings can be roughly translated into a % of VDDQ. Each horizontal tick is a different delay setting relating to a percent of a clock cycle.

2) It's color coded by failure rate, which is the number in each box. Green-> Red in terms of increasing failure rate.

3) The numbers are obtained through on silicon measurements. This excel report is generated from a script, which takes in output from a piece of firmware running on silicon. The firmware will test various combinations of VREF and delay and then report how much failing data was seen at each combination tested.

Sincerely,

Lucas

Any plans for completing the user's guide on either Jacinto or Sitara tools?

Thanks!

Greetings Lenio,

I do not have any dates for that unfortunately, but yes there will eventually be finished documentation. The main focus of development currently is getting the tooling into customer hands and ensuring all of our present and future devices are supported on the variety of customer use-cases we see.

Sincerely,

Lucas