Tool/software:

Hi, Expert

This is extension discussion from this thread,

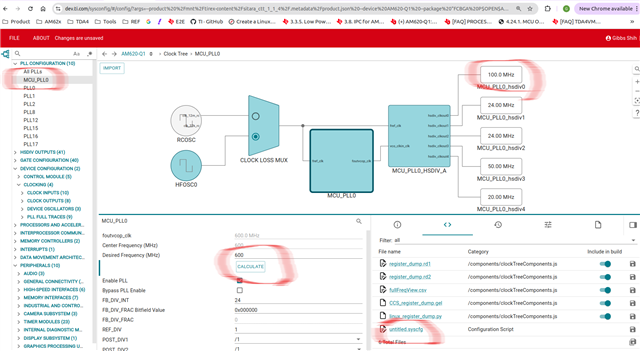

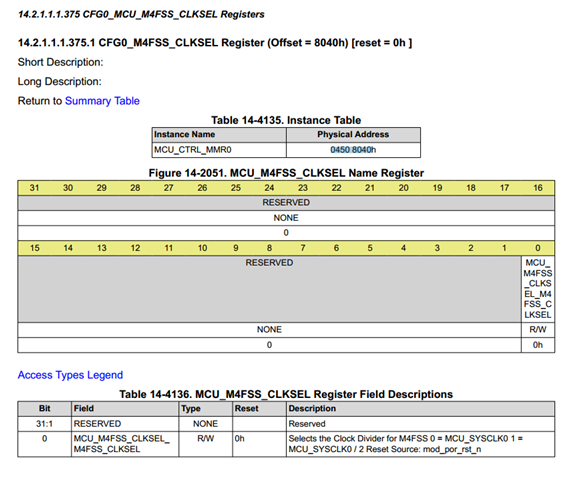

RE: AM620-Q1: Could we dynamic reduce the clock speed of the MCU M4F PLL in MCU LPM

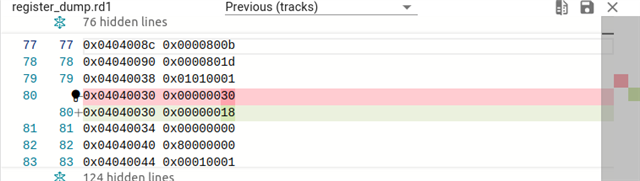

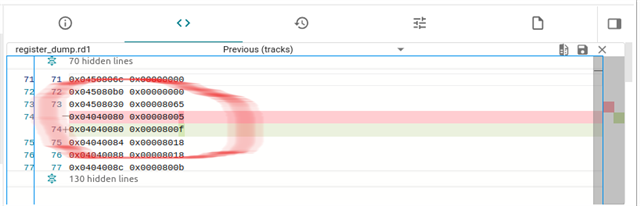

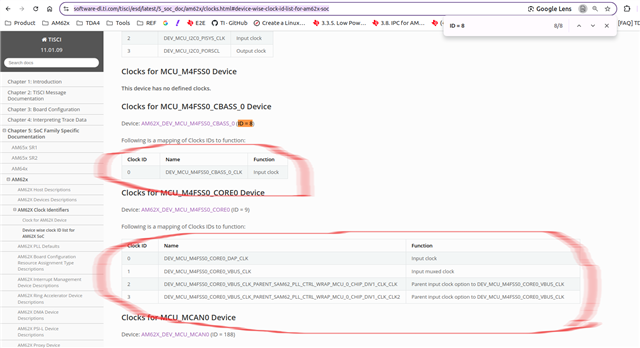

We want to reduce MCUSS operation clock to save more power in MCU LPM.

Do we have any way to modify MCUSS operation clock?

SDK : Linux 10.01.10.04

MCU SDK : 10.01.00.33

Thank You,

Gibbs