Other Parts Discussed in Thread: TPS6594-Q1, DRA829, TDA4VM

Tool/software:

Hello experts!

SDK 10

In this thread:

DRA829J: Occasional USB drops. MCU_PORz doesn't help.

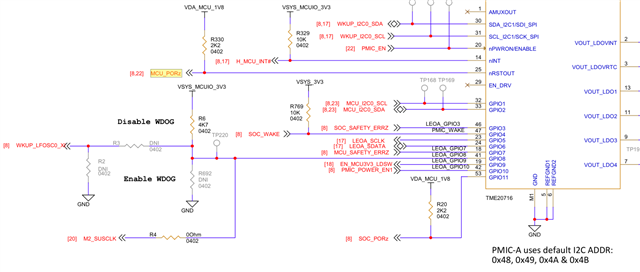

i shared our problem with USB drop outs and that triggering MCU_PORz doesn't solve the problem. In the thread we concluded that we needed to implement a PMIC reset to get the device out of the faulty state.

We have later seen issues with doing that PMIC toggling. It affects the network interfaces if done too fast, and is being dependent on leakage currents in our circuit solution.

So, my question is: How do I perform a cold reset on the DRA829V, that completely resets everything, without toggling power to the SoC?

Regards,

/Bo