Tool/software:

Hello,

I have the following question.

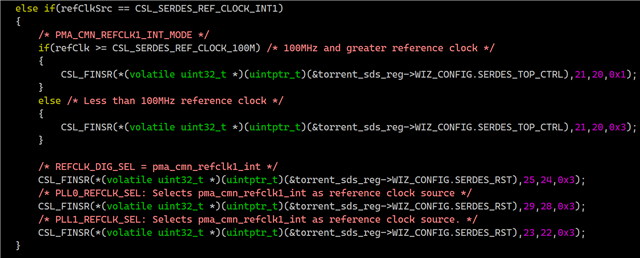

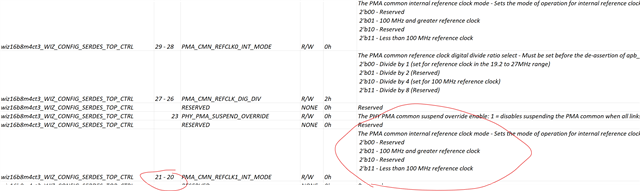

In the function CSL_serdesRefclkSel it seems that the bit PMA_CMN_REFCLK1_INT_MODE of wiz16b8m4ct3_WIZ16B8M4CT3_WIZ_CONFIG_SERDES_TOP_CTRL will only be set if the user has chosen CSL_SERDES_REF_CLOCK_INT1 as the reference clk source.

However in the description of the bitfield I do not understand the connection to the chosen reference clock. From my understanding this bit should be set as soon as you chose a ref clk with >= 100MHz.

Could you please tell me what I am missing? Thank you in advance.