Tool/software:

Dear Exparts,

Our AM6442 Prototype board has some Ethernet ports that consist of SoC's PRU ICSSG and DP83867 PHY.

We want to configure internal delay as below:

- Rx internal delay: 2 ns

- Tx internal delay: 250 ps

But, we are having trouble with these settings for the Ethernet PHY and would like to ask about the configuration process.

1. Problem

- RX Delay setting is ignored.

It is said that "RGMII mode with TX delay (configured in DTS). RX delay is not supported and has to be provided by PHY." in so we

2. AM6442 Prototype Configuration

- Processor SDK Linux for AM64X 09_00_00_03 is used.

- We tried to apply Ethernet internal delay settings with a dts like below:

/* some configs */

&icssg0_mdio {

/* some configs */

icssg0_phy2: ethernet-phy@2 {

/* some configs */

reg = <2>;

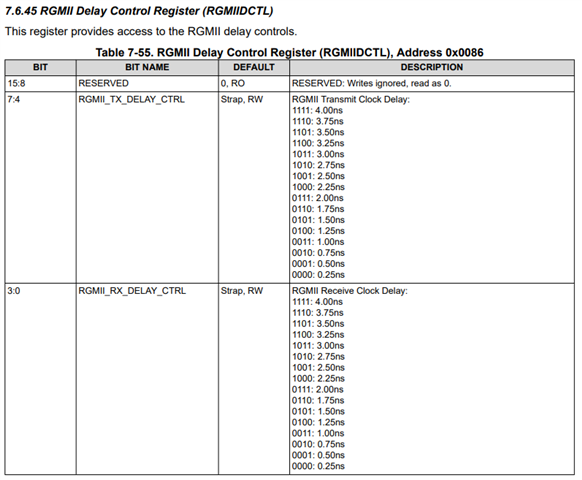

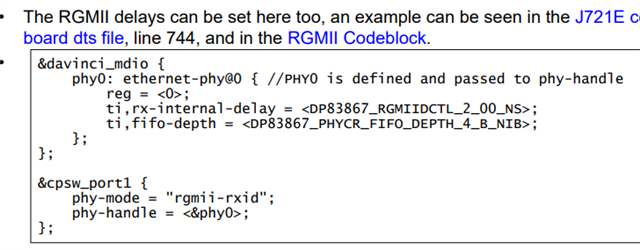

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

/* some configs */

};

icssg0_phy3: ethernet-phy@3 {

/* some configs */

reg = <3>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

/* some configs */

};

/* some configs */

};

/* some configs */

3. We would like to ask:

- A Concrete configuration method for Ethernet PHY internal delay between PRU_ICSSG and DP83867 PHY.

We understand that there are configuration constraints as described in the PRU-ICSS manual 3.6.3.3. PRU_ICSSG Ethernet — Processor SDK AM64X Documentation: "RGMII mode with TX delay (configured in DTS). RX delay is not supported and must be provided by the PHY."

Could you please explain how to configure it accordingly?

Best Regards,

Ito