Tool/software:

Hi TI experts,

Are these the steps to reset the DDR power supply(ddr_Reset func)?

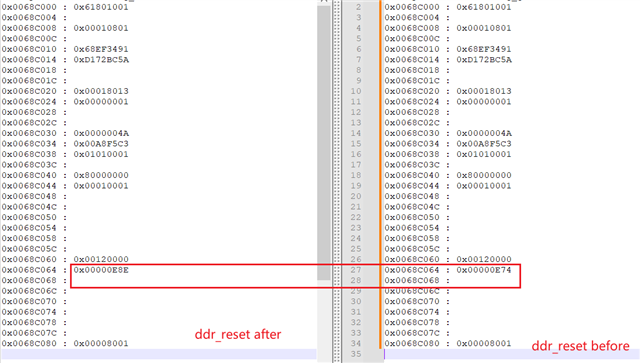

I am working on compatibility with different DDRs on SBL. When I compile different SBLs using different DDR configurations, executing memtester is normal; After successfully identifying different DDRs through the MR register in sbl, I found that memtester would fail.

I have also provided modifications for DDR compatibility, please help to check them as well.

static int32_t ddr_Reset(void)

{

Bootloader_profileAddProfilePoint("Resetting DDRSS 0721——2...\n");

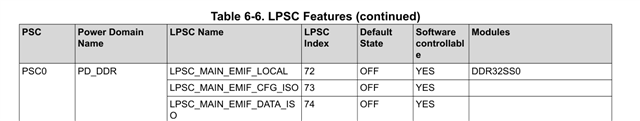

*(volatile unsigned int*)(0x400B20) = (*(volatile unsigned int*)(0x400B20) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B24) = (*(volatile unsigned int*)(0x400B24) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B28) = (*(volatile unsigned int*)(0x400B28) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B20) = (*(volatile unsigned int*)(0x400B20) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B24) = (*(volatile unsigned int*)(0x400B24) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B28) = (*(volatile unsigned int*)(0x400B28) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

return SystemP_SUCCESS;

}